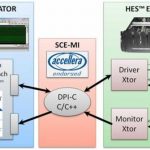

Debate rages about which approach is better for SoC design: simulation, or emulation. Simulation proponents point to software saving the need for expensive hardware platforms. Emulation supporters stake their claims on accuracy and the incorporation of real-time I/O. A few years back, some creative types coined the term SEmulation,… Read More

Author: Don Dingee

Tracing methods to multicore gladness

Multiple processor cores are now a given in SoCs. Grabbing IP blocks and laying them in a multicore design may be the easy part. While verification is extremely important, it is only the start – obtaining real-world performance depends on the combination of multicore hardware and actual application software. What should engineers… Read More

Makers get access to Intel RealSense

One of the great devices in maker lore is the Polaroid 6500 Series Sonar Ranging Module. It was originally part of the autofocus system for their SX-70 cameras circa 1978, long before through-the-lens optical autofocus sensors were perfected. Back then, people couldn’t focus. Dr. Land thought he was teaching people to compose… Read More

Lights, audio, and waiting for action from Qualcomm

The news Qualcomm has shipped over a billion Snapdragon chips in Android smartphones broke last September. After reiterating that and a sustained outlook for smartphones over the next five years, the Qualcomm CES 2015 presser seemed to leave most media outlets a bit disappointed. Naturally, that prompts us to ask what is going… Read More

SoCs should invest in a strong cache position

Like most technology firms, Apple has been home to many successes, and some spectacular defeats. One failure was Project Aquarius. At the dawn of the RISC era, before ARM architecture was “discovered” in Cupertino, engineers were hunkered over a Cray X-MP/48. The objective was to design Apple’s own quad core RISC processor to … Read More

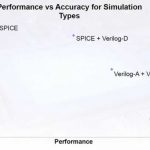

Verilog-AMS connects T-SPICE and Riviera-PRO

With advances in available IP, mixed signal design has become much easier. Mixed signal verification on the other hand is becoming more complicated. More complexity means more simulation, and in the analog domain, SPICE-based techniques grinding away on transistor models take a lot of precious time. Event-driven methods like… Read More

Lead, follow, or catch the next Silicon Valley wave

What does the IoT mean for the next wave of Silicon Valley innovators? Looking at the previous waves of semiconductor economic development and the doctrine of “creative destruction” holds clues as to how this one develops and who emerges as the new leaders.

Given seven decades of progress, it may seem semiconductor firms on top … Read More

Winning the IoT protocol battle with DSP

There are too many IoT protocols. Way too many. Anyone who says one single protocol will be the winner from end-to-end in all IoT applications and markets is smoking something. Software defined, multi-protocol gateways are the only hope on the IoT – and DSP cores enable this strategy.… Read More

Synthesizing rad-tolerant RTL for FPGAs

The maiden voyage of NASA’s Orion spacecraft brought a raft of articles about how the flight computer inside is “no smarter than your phone,” running on wheezing IBM PowerPC 750FX processors. NASA’s deputy manager for Orion avionics, Matt Lemke, admits the configuration is already obsolete – at least in commercial terms. … Read More

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era