After teams sweat the details of SoC and industrial design, they turn to printed circuit board designers for magic. Here are a pile of chips and passives, and a schematic for interconnecting them. This is how much physical space the board can occupy. Connectors have to be here, and here, and mounting holes there, and there. There … Read More

Author: Don Dingee

How many coats cover this SoC?

“Most interior paint covers with one coat.” Back when there was something called a newspaper, this was an actual blurb in the home improvement pages, section 3, part 8, page 5 of the Chicago Tribune on Sunday, August 13, 1961. Even then, marketers were catering to consumers looking to cut corners and save time, and one-coat coverage… Read More

All things being unequal for NXP and Freescale

When I read the news that NXP was buying Freescale, it felt like a part of me – and a big part of the history of high tech industry in Arizona – died. There was a time not that long ago where Motorola was the biggest employer in this state, way before Freescale and ON Semi separated from the mothership. Somehow, even with moving headquarters… Read More

New CEVA-XM4 vision IP does point clouds and more

When Intel created the OpenCV vision processing library, the idea was algorithms could take advantage of the single instruction multiple data (SIMD) capability in Intel architecture processors. (Intel’s ulterior motive is always to sell processors.) As the library has matured, optimized functions take advantage of SSE or… Read More

Mentor shows post-PC industrial device approach

The term “human machine interface” originated from the factory floor. In the context of HMI, machine refers not to the computer, but to a machine tool or other instrument the computer was attached to. For decades, if an HMI was needed, it was implemented on a PC or single-board computer running Microsoft Windows. Real-time processing… Read More

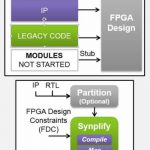

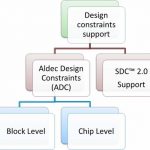

Dealing with FPGA IP in all its forms

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

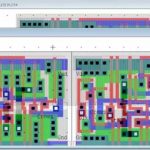

Inside tips on Tanner L-Edit toolbox

Advanced skill in auto repair, carpentry, plumbing, and similar trades often correlates to one factor. Knowing what you want to do is one thing – having the proper tool is another, and can make the difference. Many a job has extended from minutes to hours over the lack of the right tool at the right moment. Experienced mechanics and… Read More

Xilinx ships the VU440 and its 4M logic cells

Xilinx has delivered not only “the biggest FPGA on the planet”, but what it claims is currently the world’s largest integrated circuit: the Virtex UltraScale VU440, with 19 billion transistors fabbed in TSMC 20nm. The list of first customers to receive parts says a lot about the state of SoC design today, and the vital role FPGA-based… Read More

How Imagination tested the PowerVR Series6XT

We have been hearing for some time about the Synopsys HAPS-70 and how they have co-created the hardware and software architecture for FPGA-based prototyping with their customers. Now, we see details published by Synopsys on how they collaborated with Imagination on the design of the PowerVR Series6XT GPU.

The first thing to come… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era