Edmond Macaluso, President of Z-Circuit Automation met with me at DAC on Tuesday afternoon to provide an overview of how their EDA tools characterize cell libraries. … Read More

Author: Daniel Payne

Double Patterning Technology at DAC

David Abercrombie from Mentor Graphics met with me on Tuesday at DAC to provide an update on DPT – Double Patterning Technology, something new required for several layers starting at the 20nm node in order to get any IC yield. DPT is also part of Multiple-Patterning.… Read More

Custom IC Layout Automation at DAC

Three people from Ciranova met with me at DAC this year: Eric Filseth (CEO), David Millman (Marketing) and Lindor Hendrickson (CTO). They gave me an update on how the Helix tools are being used to automate the layout of custom IC designs at 28nm and smaller nodes.… Read More

IPL Alliance at DAC

Lunch on Tuesday at DAC was sponsored by the IPL Alliance and thankfully this year they skipped the attempt at humor and focused on interoperable PDKs. Presenting companies include: Synopsys, Dongbu HiTek, TowerJazz, X-FAB and Si2. Having both OpenPDK and iPDK on the same platform does sound like a peaceful co-existence to me,… Read More

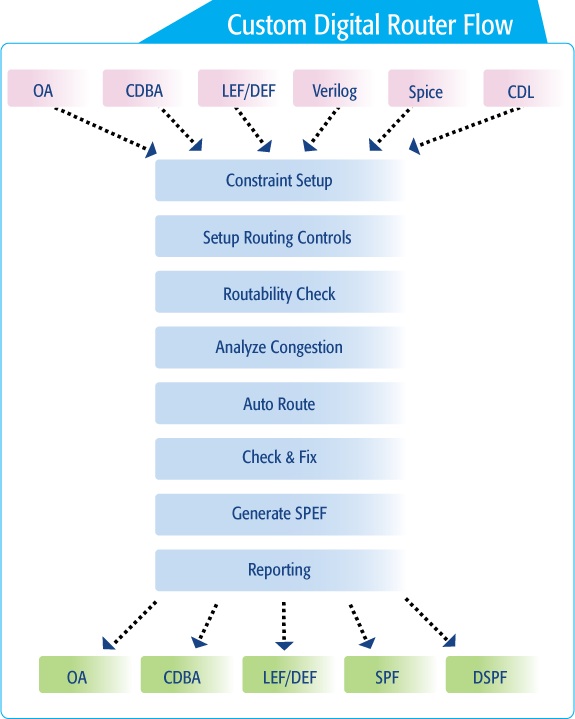

Shape-based IC Routing at DAC

IC place and route is a big challenge so we see many EDA companies creating tools. On Tuesday at DAC I met with Dave Noble of Pulsic to get an update.

Notes

Dave Noble, VP Operations (EDA since 2003), Sperry Univac since 1974

– had been an EDA distributor for Pulsic as well

More leads qualified on Monday than all days of last year … Read More

3D Thermal and Mechanical Stress for IC Packaging

3D has been a growing buzz word in IC design and packaging for several years now, so it’s refreshing to actually find an EDA vendor that has developed tools to help analyze something like 3D thermal and mechanical stress at DAC. … Read More

Analog Macromodels at DAC

I use social media 7 days a week and while at DAC I received a message from Herve Guegan on my LinkedIn account where he basically said, “Hey, go check out Asygn at DAC, they do analog macro models.”… Read More

What’s new with HSPICE at DAC?

One year ago I met with Hany Elhak of Synopsys to get an update on what was new with HSPICE in 2011, so this year at DAC Hany met me at the Synopsys booth for a quick update.

HSPICE has something called Precision Parallel so with 16 cores your IC circuit simulations will have about 10 x speed up compared to a single core.… Read More

Samsung, Synopsys, GLOBALFOUNDRIES and ARM at DAC

Tuesday morning at DAC I attended the Synopsys-hosted breakfast to hear from foundries and ARM about the challenges of designing and delivering silicon at the 32nm/28nm and 20nm nodes.

… Read MoreFast Monte Carlo from Infiniscale at DAC

Firas Mohamed, President and CEO (Ph.D.) of Infiniscale met with me on Monday at DAC to provide an overview of what EDA software they offer to IC designers at the transistor-level.

Vision – analog flow that Monte Carlo simulation is required, which is thousands of circuit simulations, however the higher the sigma the more… Read More

Solving the EDA tool fragmentation crisis