My new iPad lasts about 10 hours on a single charge and the A5X processor is designed with a 45nm process from Samsung. Processor chips for tablets like this use a multi-voltage IC design flow to reduce total power by:… Read More

Author: Daniel Payne

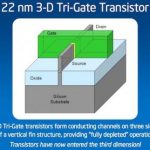

Designing with FinFETs

Intel is the number one semiconductor company in the world and has taken the lead in bringing FinFET (aka Tri-Gate) silicon to market at the 22nm node starting in May 2011, so now we see the pure play foundries playing catch-up and start talking about their own FinFET roadmaps. IC designers and layout engineers want to know how their… Read More

EDA User: Rafaela Novais from TowerJazz Semi

While reading an article on DeepChip I found an interesting comment from Rafaela Novais, a Design Support Manager at TowerJazz Semi and decided to interview her to learn more about her experience as an IC designer and EDA tool user.

EDA Solutions at Ultra Low Power Developer Forum Demonstrates Mixed-Signal Flow including Tools from Tanner EDA, Incentia and Aldec

EDA Solutions, sole representative in Europe for Tanner EDA and Incentia Design Systems, is exhibiting at the ‘Design & Elektronik’ Developer Forum on Ultra Low Power in Munich, Germany, on October 10, 2012, at the Holiday Inn (Munich – City Centre).

EDA Solutions will be presenting its complete analog, digital and… Read More

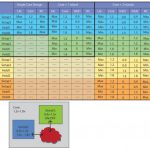

EDAC Reports Upbeat Q2 2012 Revenues

EDA revenues for Q2 2012 were up 10.8% compared to Q2 2011 as reported by EDAC today.

Increasing

- CAE

- IC Physical Design & Verification

- Semi IP

High Frequency Analysis of IC Layouts

IC designers of passive devices often use empirical approaches to perform High Frequency Analysis (HFA), however there is at least one new approach being offered by Mentor Graphics using a tool flow of:

- Device detection and extraction with Calibre LVS and Calibre PERC

- Interconnect RLC extraction with Calibre xRC, Calibre xACT-3D

User Review: iOS 6 on iPad

Much has been written about the new iPhone 5 and iOS 6 in terms of the features, specifications, bill of materials, and chips used in the design. Today I’ll share my experiences of actually using the new iOS 6 on iPad as an EDA blogger.

Upgrading to iOS6

Clicking the On button and noticing that the App Store icon has something new,… Read More

A Brief History of RTL Design

RTL is an acronym for Register Transfer Level and refers to a level of hardware design abstraction using Registers and logic gates. Here’s an example schematic showing one DFF as a register, and one inverter as a logic gate.

Figure 1: RTL diagram of a DFF (D Flip Flop) and Inverter… Read More

Mentor Graphics Update at TSMC 2012 OIP

What

In just 20 days you can get an update on four Mentor Graphics tools as used in the TSMC Open Innovation Platform (OIP). Many EDA and IP companies will be presenting along with Mentor, so it should be informative for fabless design companies in Silicon Valley doing business with TSMC.

… Read More

Displaced but Looking to Add EDA Tools Skills?

In this tough economy you may find yourself displaced and looking for the next opportunity. If you’d like to add some new EDA tool skills, then check out what EMA Design Automation is offering with free Cadence OrCAD training.… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?