I love all things SPICE so when I read a tweet tonight from @PartSimI just had to try out their Schematic Capture and SPICE circuit simulator in a browser. The site is www.partsim.com and all you need is a web browser and short registration process, then it’s off to the Examples where I found a simple CMOS inverter and then extended… Read More

Author: Daniel Payne

Engineer to Engineer, Embedded Instrumentation

Last month the folks at Tektronix did something very useful, they invited 30 engineers to talk directly with their chief engineer of embedded instrumentation as part of “Meet the Experts” in Santa Clara, CA.

Brad Quinton, Chief Architect created a new and efficient approach of embedding instrumentation in your … Read More

Phablet, e-reader, Nexus

In November and December I upgraded three devices and share my opinions on the utility of each:

- Samsung Galaxy Note (aka Phablet = Phone + Tablet)

- Kindle Paperwhite (e-reader)

- Google Nexus 7 (Tablet)

IP Scoring Using TSMC DFM Kits

Design For Manufacturing (DFM) is the art and science of making an IC design yield better in order to receive a higher ROI. Ian Smith, an AE from Mentor in the Calibre group presented a pertinent webinar, IP Scoring Using TSMC DFM Kits. I’ll provide an overview of what I learned at this webinar.… Read More

FinFET Modeling and Extraction at 16-nm

In 2012 FinFET is one of the most talked about MOS technologies of the year because traditional planar CMOS has slowed down on scaling below the 28nm node. To learn more about FinFET process modeling I attended a Synopsys webinar where Bari Biswas presented for about 42 minutes include a Q&A portion at the end.

Bari Biswas, Synopsys… Read More

A Comparison of SemiWiki and DeepChip

An email update from John Cooley at DeepChip this morning prompted the bloggers here at SemiWiki to continue the discussion and point out incorrect data, so that readers realize what is really happening with our media portals as sources of timely and relevant news and opinion. I respect what John Cooley has done with DeepChip over… Read More

Schematic Capture and SPICE from Symica

At DAC in June I first blogged about Symicabecause they offered a Fast SPICE circuit simulator, and today I discovered a free version so I decided to write up a mini-review for you.… Read More

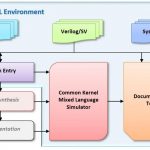

An FPGA Design Flow with Aldec Tools

I’ve used FPGA vendor-supplied tools from both Xilinxand Lattice Semibefore, so I wanted to see what EDA tools Aldec has to offer for FPGA design. I read the Aldecwhite paper, Corporate Standardization of FPGA Design Flow, and summarize what I found.… Read More

Mixed-Signal Methodology Guide: Design Management

I reviewed the book Mixed-Signal Methodology Guidein August of this year published by Cadence, and decided to follow up with one of the authors, Michael Henrie from ClioSoft, to learn more about the importance of Design Management for AMS. Michael is a Software Engineering Manager at ClioSoft and has worked at Zarlink Semi, Legerity,… Read More

Variation-Aware Design: A Hands-on Field Guide

IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior