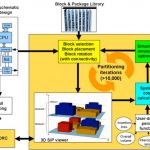

We blog a lot about Moore’s Law, and even “More than Moore” where 3D integration of ICs and systems are used to get lower product costs. One big challenge with 3D integration of ICs is that most EDA software was really intended only for abstracting at 2D or 2.5D structures. Over the past several years there have … Read More

Author: Daniel Payne

Five Areas at #53DAC That Require Your Contribution

The 53rd DAC (Design Automation Conference) is some 8 months away, however to make this conference and exhibit another success requires planning, people and awareness. That’s where you come in, because you can contribute your expertise in five different areas:

[LIST=1]

12 Reasons to Attend this Annual User Group Meeting for Transistor-level IC Designers

My first job out of college was transistor-level circuit design of DRAMs at Intel, so I’ve continued to be fascinated with both the craft and science of designing, optimizing, verifying and debugging custom ICs. Last October I traveled to Munich, Germany to attend a two day user group meeting for engineers using tools from… Read More

Phablet Impact on PC Sales

Apple iPhone 6 and 6s users are recent converts to the latest growth trend in smart phones, large screens at 5.5″ in size and aiming even higher each year. I’ve owned a 5.5″ smart phone from Samsung for some 3 years now, so have immensely enjoyed the larger screen size to get my daily work done with: web browsing, … Read More

The Future of Moore’s Law

I’ve lived in Silicon Valley then moved north to the Silicon Forest (aka Portland, Oregon) in 1995, and thankfully we have a lot of high-tech companies here like: Intel, Lam Research (Novellus), Lattice Semi, Qorvo, Synopsys, Mentor, Cadence, Northwest Logic, etc. There’s a global industry organization called… Read More

Thermal Reliability and Power Integrity for IC Design

When I designed DRAM chips at Intel back in the 1970’s we didn’t really know what the die temperature would be before taping out silicon, instead we waited for packaged parts to come back and then did our thermal measurements. IC designers today don’t have that luxury of taping out their new SoC without having … Read More

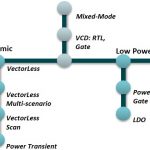

Breakthrough Battery Life for Mobile Devices

Battery life is a never-ending battle for me with all of my mobile devices: Laptop, Tablet, Smart phone, bike computer, Kindle Reader, Bluetooth headset, etc. It seems like I’m constantly having to charge up my battery at the most inconvenient times. When I think about the history of batteries for mobile devices I can recall… Read More

Who is Leading in the Wearables Market?

My first experience with a wearable device was back in 1978 at college, it was an LED-based watch that had you push a button to read the time of day, saving battery life. Sad to say, but that electronic watch didn’t make it through the January winter at the University of Minnesota, so was promptly returned for a refund. Fast forward… Read More

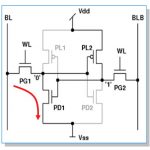

Optimizing SRAM IP for Yield and Reliability

My IC design career started out with DRAM at Intel, and included SRAM embedded in GPUs, so I recall some common questions that face memory IP designers even today, like:

- Does reading a bit flip the stored data?

- Can I write both 0 and 1 into every cell?

- Will read access times be met?

- While lowering the supply voltage does the cell data retain?

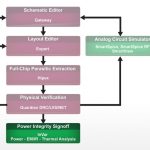

Why You Really Need Chip-Package Co-analysis

There’s only one software company that I know of that covers four major disciplines: Fluids, Structures, Electronics and Systems. That company is ANSYS and when they acquired Apache Design Automation back in 2011 they filled out their products for electronics design, and more specifically in the area of integrated chip-package… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?