Small EDA companies often focus on a single point tool and then gradually over time they add new, complementary tools to start creating more of a sub-flow to help you get that next SoC project out on time. The most astute EDA companies often choose to partner with other like-minded companies to create tools that work together well,… Read More

Author: Daniel Payne

TCAD Simulation of Organic Optoelectronic Devices

In my office there are plenty of LED displays for me to look at throughout the day: three 24″ displays from Viewsonic, a 15″ display from Apple, an iPad, a Samsung Galaxy Note 4, a Nexus tablet, a Garmin 520 bike computer, and a temperature display. LED and OLED displays are ubiquitous in all sorts of consumer electronics,… Read More

Analog, Low-power Optimization at SMIC

Talking with actual IC designers is always fascinating to me, because these engineers are the unsung heroes that enable our modern day world of consumer and industrial electronics. Too often we only hear from the CEO or other C-level executives in the press about their own companies, products, services and vision. I recently had… Read More

CES 2017, Semiconductors and Cycling

It’s back, that giant consumer electronics trade show CES 2017, held every January in Las Vegas with too many new product introductions to mention in one blog, so I’ll take a more focused look at what’s new for cycling.

Smart Bike

We all know what a smart phone is, but what could a smart bike be? The Chinese company… Read More

Solving a Murder Case with IoT Devices

I watch a lot of Netflix and there are so many detective movies and series for me to enjoy where I try and match wits with the bad guys and figure out who is guilty a few seconds before the law enforcement characters do. On TV and with our movies there is often critical evidence extracted from desktop computers, laptops, hard drives, smart… Read More

Real Time Virtualization, How Hard Can it Be?

My first exposure to running something virtual on a computer was when I decided to run the Windows OS on my MacBook Pro using software provided by Parallels. With that virtualization I was able to run the Quicken app under Windows on my MacBook Pro, along with the popular Internet Explorer web browser. The app performance on virtualized… Read More

Driverless Cars and our Global Economy

While traveling to California this year I had my first Uber trip after a concierge in Santa Clara recommended it as the best way to get to the airport, instead of the usual and expensive taxi ride. Later in the year I had my first Lyft ride after my road bike broke down and I needed a ride back home. Our transportation choices are shifting,… Read More

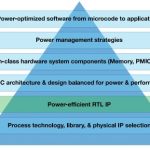

How ARM designs and optimizes SoCs for low-power

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

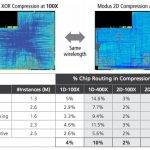

Reducing the Cost of SoC Testing

Every year certain technology themes appear, like at ITC this year a big theme was how to reduce the cost of SoC testing. I spoke with Rob Knoth of Cadence by phone to hear more about this cost of test theme. Rob gave me an example of an SoC that takes 27 seconds on a tester, so at $0.04 per second in test costs amounts to $1.08 per part. If you… Read More

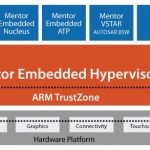

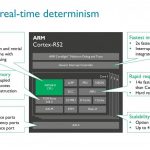

ARM and Mentor talk about Real Time Virtualization, Webinar

Processor cores come in a wide variety of speeds, performance and capabilities, so it may take you some time to find the proper processor for your system. Let’s say that you are designing a product for the industrial, automotive, military or medical markets that has an inherent requirement for safety, security and reliability… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?