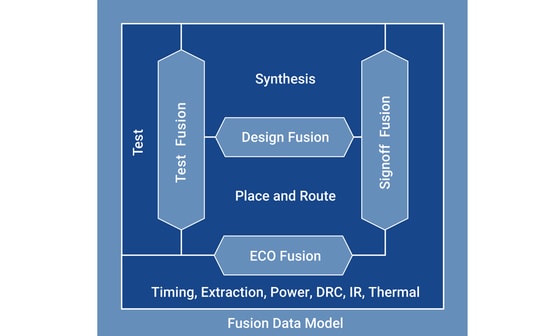

Synopsys is pretty well-known for their early entry into logic synthesis with the Design Compiler tool and more recent P&R tool with IC Compiler, so I met up with two folks at DAC to get a better idea of what this new Fusion technology was all about where the barriers between tools are changing. Michael Jackson and Rahul Deokar … Read More

Author: Daniel Payne

Improving Yield and Reliability with In-Chip Monitoring, there’s an IP for that

There’s an old maxim that you can only improve what you measure, so quality experts have been talking about this concept for decades and our semiconductor industry has been the recipient of such practices to such an extent that we can now buy consumer products that include chips with over 5 billion transistors in them. You’ve… Read More

The Pain of Test Pattern Bring-up for First Silicon Debug

In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

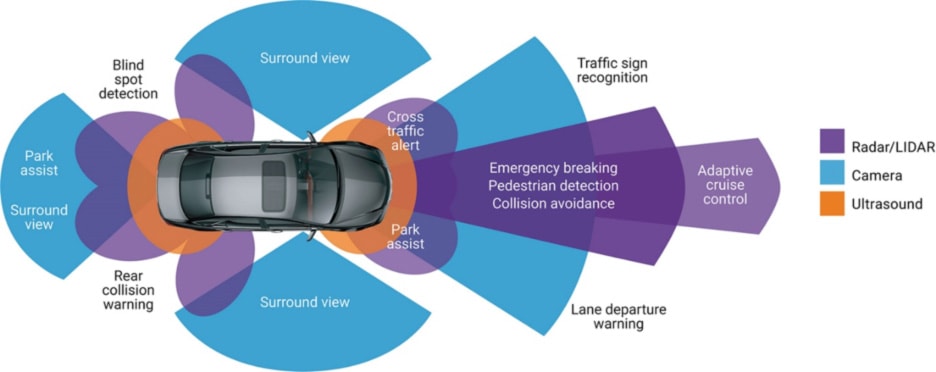

Networking trends for Automotive ADAS Systems

From my restaurant seat today in Lake Oswego, Oregon I watched as an SUV driver backed out and nearly collided with a parked car, so I wanted to wave my arms or start shouting to the driver to warn them about the collision. Cases like this are a daily occurrence to those of us who drive or watch other drivers on the road, so the promises of… Read More

Meeting Analog Reliability Challenges Across the Product Life Cycle

Create a panel discussion about analog IC design and reliability and my curiosity is instantly piqued, so I attended a luncheon discussion at #55DAC moderated by Steven Lewis of Cadence. The panelists were quite deep in their specialized fields:… Read More

Cadence Update on AMS Design and Verification at #55DAC

As a blogger in the EDA industry I get more invitations to meet with folks at DAC than I have time slots, so I have to be a bit selective in who I meet. When the folks at Cadence asked me to sit down and chat with Mladen Nizic I was intrigued because Mladen is so well-known in the AMS language area and he’s one of the authors of, The Mixed-Signal… Read More

AMS Experts Share IC Design Stories at #55DAC

At #55DAC in SFO the first day is always the busiest on the exhibit floor, so Monday by lunch time I was hungry and took a short walk to the Marriott hotel nearby to listen to AMS experts from several companies talk about their EDA tool use, hosted by Synopsys:

- Samsung

- Toshiba Memory Corp.

- NVIDIA

- Seagate

- Numem

- Esperanto

Daniel’s #55DAC Trip Report

Another year, another DAC, and last month it was #55DAC in SFO and the first thing that I noticed was that the event was no longer located in the traditional North or South Halls, rather we were in the smaller, Moscone West on two floors, almost like a 3D FinFET. Checkin to get my badge was highly automated and oh so fast, well done.… Read More

Optimization and Reliability for FinFET designs at #55DAC

TSMC is the leading foundry worldwide and they make a big splash each year at the DAC exhibit and conference, so I stopped by their theatre area during the presentation from IP vendor Moortec to see what’s new this year. Stephen Crosher was the presenter from Moortec and we had exchanged emails before, so this was the first time… Read More

A New Kind of Analog EDA Company

My IC design career started out with circuit design of DRAMS, so I got to quickly learn all about transistor-level design at the number one IDM in the world, Intel at the time. In the early days, circa 1978 we circuit designers actually had few EDA tools, mostly a SPICE circuit simulator followed by manual extraction, manual netlisting,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?