The IC design and verification process can be comprised of many independent point tools, or for more synergy you can have tools that work together by a more synergistic process. We’ve all heard the maxim, “Work smarter, not harder.” A white paper just came out from Methodics on a smarter approach, Traceability… Read More

Author: Daniel Payne

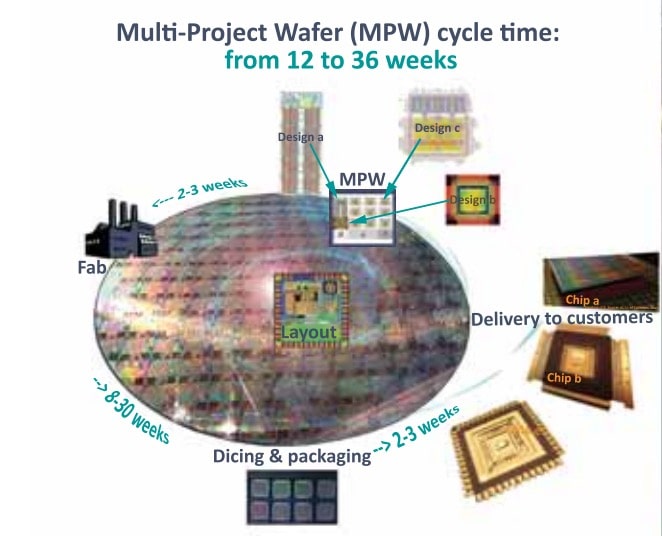

Ultra low-power Analog Design using a Multi-Project Wafer approach

On SemiWiki we often talk about bleeding-edge technology like 7nm, 5nm or even 3nm, but for analog IC designs there’s a low-cost alternative to getting your ideas validated and prototyped without taking out a multi-million dollar loan, and that’s through the use of Multi-Project Wafers (MPW). Starting with a mature… Read More

Data Centers and AI Chips Benefit from Embedded In-Chip Monitoring

Webinars are a quick way to come up to speed with emerging trends in our semiconductor world, so I just finished watching an interesting one from Moortec about the benefits of embedded in-chip monitoring for Data Center and AIchip design. My first exposure to a data center was back in the 1960s during an elementary school class where… Read More

How Well Did Methodics do in 2018?

In January I read from the ESDA Allianceabout EDA and Semiconductor IP revenues increasing 6.7% for Q3 2018, reaching $2,435.6 million, which is decent growth for our maturing industry. In stark contrast there’s a company called Methodicsthat specializes in Intellectual Property Lifecycle Management (IPLM) and traceability… Read More

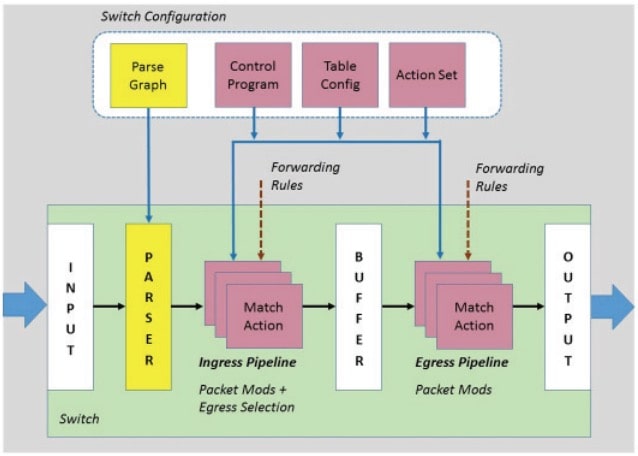

Verifying Software Defined Networking

I’ve designed hardware and written software for decades now, so it comes as no surprise to see industry trends like Software Defined Radio (SDR) and Software Defined Networking (SDN) growing in importance. Instead of designing a switch with fixed logic you can use an SDN approach to allow for greatest flexibility, even … Read More

AI, Deep Learning, SystemC, UVM, PSS – DVCon Has it All

Today I had the pleasure to speak with Tom Fitzpatrick, TPC Chair for the DVCon conferenceand exhibition slated for February 25-28 in the heart of Silicon Valley – San Jose. Tom lives in Massachusetts, a place where I used to live and work at Wang Labs, back in the day before the PC and WordPerfect software ended Wang’s… Read More

Where Circuit Simulation Model Files Come From

I started out my engineering career by doing transistor-level circuit design and we used a proprietary SPICE circuit simulator. One thing that I quickly realized was that the accuracy of my circuit simulations depended entirely on the model files and parasitics. Here we are 40 years later and the accuracy of SPICE circuit simulations… Read More

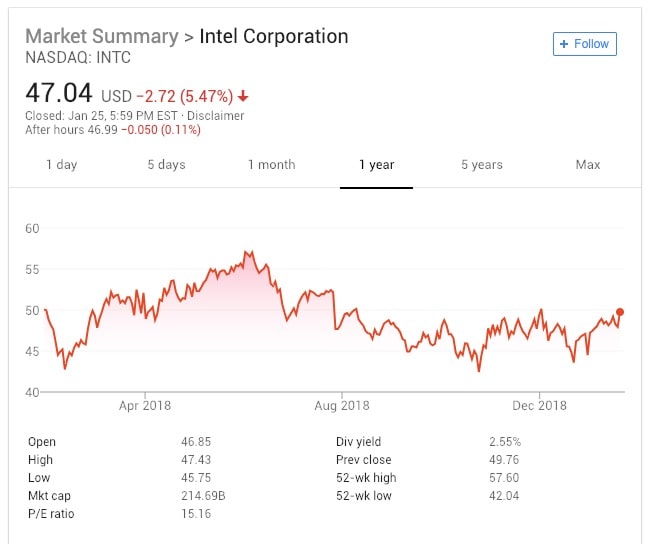

The 50th Year of Intel, What Happened in 2018

2018 was the 50th year for Intel in the semiconductor business, and their Q4 2018 conference call just happened last week, so I’ll get you all caught up on what they talked about. Bob Swan is the CFO and interim CEO, as the company continues to search for a new CEO after Brian K. was ousted for misconduct. Here’s a quick financial… Read More

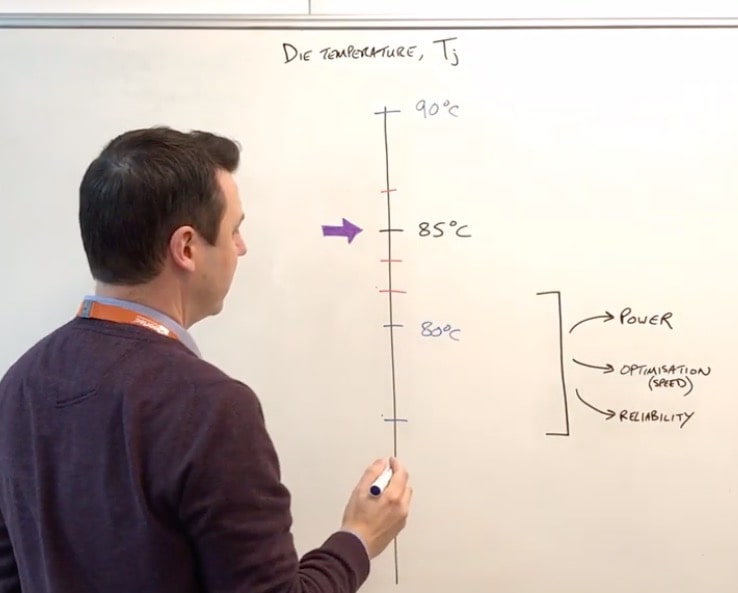

Accuracy of In-Chip Monitoring for Thermal Guard-banding

I remember working at Intel and viewing my first SPICE netlist for a DRAM chip, because there was this temperature statement with a number after it, so being a new college graduate I asked lots of questions, like, “What is that temperature value?”

My co-worker answered, “Oh, that’s the estimated junction… Read More

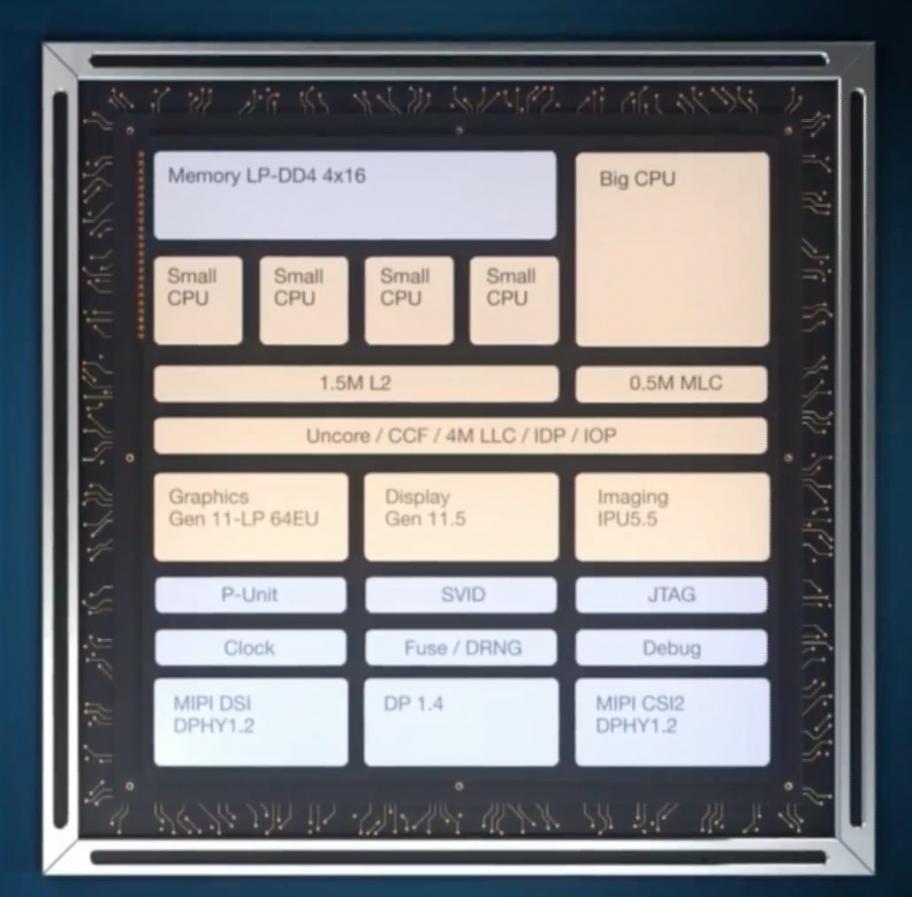

Intel Swaggers at CES

Intel started out as a DRAM company using planar NMOS technology, then later on added EPROM and Microprocessors to the product mix. Their CPU technology enabled the dynamic growth of the PC industry starting with the IBM PC back in 1981 and continuing all of the way to this day. They long ago dropped out of the DRAM marketplace and began… Read More

Beyond Moore’s Law: High NA EUV Lithography Redefines Advanced Chip Manufacturing