I first connected with Gerhard Angst of Concept Engineering over 15 years ago, because I was using their SpiceVision PRO tool to visual SPICE netlists received from customer designs to be debugged in a FastSPICE circuit simulator. The ability to visualize a transistor-level netlist was simply essential to quickly understanding… Read More

Author: Daniel Payne

#56DAC – Functional Safety Panel hosted by Mentor

Four experts in the discipline of functional safety were gathered together at #56DAC in Vegas earlier in June, hosted at the Mentor booth, so I rested my legs and typed notes as fast as I could. The product areas that I first think about when functional safety (FuSa) comes up are automotive, medical and aerospace, because keeping… Read More

#56DAC – What’s New with Custom Design Platform

TSMC attends DAC every year and they do something very savvy, it’s a theatre where they invite all of their EDA and IP partners to present something of interest, followed by a drawing for a prize. At the end of the day they even have a nice prize, like a MacBook Air, which I didn’t win. On Wednesday I watched Dave Reed of Synopsys… Read More

#56DAC – Machine Learning and its impact on the Digital Design Engineer

Tuesday for lunch at #56DAC I caught up to the AI/ML experts at the panel discussion hosted by Cadence. Our moderator was the affable and knowledgable Prof. Andrew Kahng from UC San Diego. Attendance was good, and interest was quite high as measured by the number of audience questions. I learned that EDA tools that use heuristics… Read More

#56DAC – Panel Discussion: Closing Analog and Mixed-Signal Verification in 5G, HPC and Automotive

Monday afternoon at #56DAC I enjoyed attending a luncheon panel discussion from four AMS experts and moderator, Prof. Georges Gielen, KU Leuven. I follow all things SPICE and this seemed like a great place to get a front-row seat about the challenges that only a SPICE circuit simulator can address. Here’s a brief introduction… Read More

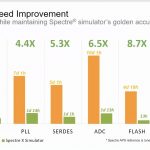

Parallel SPICE Circuit Simulator Debuts

In EDA the most successful companies will often re-write their software tools in order to add new features, improve accuracy, increase capacity and of course, shorten run times. For SPICE circuit simulators we typically look at several factors to see if a new tool is worth a look or not:

- Netlist compatibility

- Model support

- Foundry

Needham is Upbeat about EDA and IP Growth at #56DAC

It’s Sunday afternoon and I just attended the annual Needham presentation at #56DAC in sunny Las Vegas, where Rich Valera shared an upbeat view of EDA and IP growth. Here are the five drivers of this growth:

- IoT

- Automotive

- Webscale/FAANGs

- AI/ML

- China

For the IoT market they’ve seen a CAGR of 8.6% to $8.2B in 2018, projected… Read More

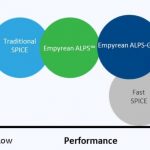

The Changing Landscape for SPICE Circuit Simulators

I first started using a SPICE circuit simulator in 1978 while at Intel and have followed that market ever since then. Back at DAC in 2012 I first heard of a Chinese EDA company called IC Scape with a SPICE circuit simulator called Aeolus, so I blogged about it. Fast forward to 2019 and I heard from Ravi Ravikumar, a former co-worker from… Read More

Semiconductor IP Security Issues

Every morning I read the headlines from SemiWiki, CNN, LinkedIn and my Twitter feed, and it seems like every week that I read about another security breach that makes me wonder if anything online is secure. Companies try to harden their web sites, IT infrastructure and even their electronic products from being exploited or tampered… Read More

Automotive Design and Virtual Prototyping

The entire history of EDA software tools has enabled engineers to design ICs and SoCs using virtual prototyping, so most of us in the industry are familiar with the idea of modeling and simulating something as complex as an IC before actually starting the manufacturing process. In a complex system like an automobile there are a lot… Read More

Beyond Moore’s Law: High NA EUV Lithography Redefines Advanced Chip Manufacturing