In part one of this webinar series, Keysight and Modelithics looked at the use of 3D passive vendor component models supporting highly accurate, automated 3D EM-circuit co-simulation of high-frequency RF board designs. Part two continues the exploration of RF board design flows for simulating active circuits on boards, again… Read More

Search Results for "beth martin"

Sondrel Redefines the AI Chip Design Process

Designing custom silicon for AI applications is a particularly vexing problem. These chips process enormous amounts of data with a complex architecture that typically contains a diverse complement of heterogeneous processors, memory systems and various IO strategies. Each of the many subsystems in this class of chip will … Read More

Perforce IP and Design Data Management #61DAC

I recall first blogging about Helix IPLM (formerly Methodics IPLM) at DAC in 2012, then Perforce acquired the company in July 2020, so I stopped by the Perforce booth this year at DAC to get an update from Martin Hall, Principal Solutions Engineer at Perforce. Martin’s background includes working at Dassault Systemes, Synchronicity,… Read More

Synopsys is Paving the Way for Success with 112G SerDes and Beyond

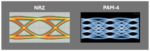

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes… Read More

ASML- Soft revenues & Orders – But…China 49% – Memory Improving

ASML- better EPS but weaker revenues- 2024 recovery on track

China jumps 10% to 49%- Memory looking better @59% of orders

Order lumpiness increases with ASP- EUV will be up-DUV down

“Passing Bottom” of what has been a long down cycle

Weak revenues & orders but OK EPS

Reported revenue was Euro5.3B and EPS of Euro3.11… Read More

PCI-SIG DevCon and Where Samtec Fits

PCIe (peripheral component interconnect express) is an interface standard for connecting high-speed components contained in PCs, MACs and other types of processors. Think graphics, storage arrays, Wi-Fi and the like. This communication standard has become incredibly popular. The first version of the standard was released… Read More

WEBINAR: Secure messaging in a post-quantum world

In a recent marketing campaign, WhatsApp (and by extension, its parent company Meta) mocks the ubiquitous but unsecure messaging vehicle, SMS, saying anyone can read plain texts and mobile users should use some means of secure messaging. Apps like WhatsApp, Messenger, iMessage, and WeChat have each attracted over 1 billion … Read More

Report from SPIE- EUV’s next 15 years- AMAT “Sculpta” braggadocio rollout

-We attended the SPIE lithography Conference in San Jose

-No significant news or announcements on EUV

-Focus on 500WPM target and High & Hyper NA rollout

-AMAT overblown Sculpta-Not exactly what its cracked up to be

SPIE Lithography 2023

We have been attending SPIE for many years now and are happy to see a return to pre Covid levels… Read More

U.S. Automakers Broadening Search for Talent and R&D As Electronics Take Over Vehicles

The auto industry isn’t for the faint of heart in late 2022. As Deloitte recently explained, chip shortages, supply chain bottlenecks, unpredictable consumer demand and the industry overhaul mandated by the rise of EVs are all creating unprecedented turmoil in this key sector. One particularly pressing challenge is the ongoing… Read More

Upcoming Webinar: Optimized Chip Design with Main Processors and AI Accelerators

Using the right tool for the job can be extremely important. Well, maybe not in the case of the famed chef Martin Yan who is notorious for using just one knife—a razor sharp wide blade cleaver that doubles as a spatula—for preparing anything and everything he cooks. For the rest of us, though, the right tools can make all the difference.… Read More

TSMC N3 Process Technology Wiki