You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Search Results for "beth martin"

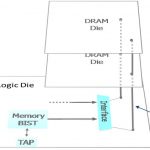

3D ICs complicate silicon testing, but solutions exist now to many of the key challenges. – by Stephen Pateras

The next phase of semiconductor designs will see the adoption of 3D IC packages, vertical stacks of multiple bare die connected directly though the silicon. Through-silicon vias (TSV) result in shorter and thinner… Read More

Wyatt Earp probably wasn’t thinking of OPC when he said, “Fast is fine, but accuracy is everything,” but I’ll adopt that motto for this discussion of full-chip OPC and post-OPC verification models.

Accuracy is the difference between the calibrated model prediction and the calibration wafer result. Accuracy depends on several… Read More

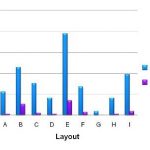

With the adoption of the 32/28 nm process node, some significant new challenges in digital routing arise—including complex design rule checking (DRC) and design for manufacturing (DFM) rules, increasing rule counts, very large (1 billion transistor) designs. To meet quality, time-to-market, and cost targets, design teams… Read More

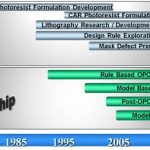

For an industry committed to constant innovation, changes in any part of the design flow are only slowly adopted, and only when absolutely necessary. Almost 10 years ago, it became clear that shrinking process technologies would bring a massive growth of layout and mask data—rougly 50% per node. This avalanche of data seriously… Read More

In part I of this series, we looked at the history of lithography process models, starting in 1976. Some technologies born in that era, like the Concorde and the space shuttle, came to the end of their roads. Others did indeed grow and develop, such as the technologies for mobile computing and home entertainment. And lithography … Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot