I recall first blogging about Helix IPLM (formerly Methodics IPLM) at DAC in 2012, then Perforce acquired the company in July 2020, so I stopped by the Perforce booth this year at DAC to get an update from Martin Hall, Principal Solutions Engineer at Perforce. Martin’s background includes working at Dassault Systemes, Synchronicity, Innoveda and Texas Instruments. The four big messages this year were:

- Managing costs and footprint in an AI world

More effective management of costs through IP-centric design practices and managing/enforcing traceability for high value IP — such as AI GPUs and cores, and low power components — to help reduce power running costs and footprints. - The critical need for AI data set management

AI depends on curating large amounts of data on which to train models, but this data needs to be reviewed and cleaned to avoid pollution. Plus, new data needs to be onboarded in a measured way, and secondary data sets need to be weighted to influence AI outcomes appropriately. - Plans for the commoditization of AI

As the world of AI designs evolve, expect to see a move away from proprietary models to third-party AI solutions (standard AI processing units) that can be used as building blocks. Efficiently managing the AI IP supply chain is going to be vital, to reduce complexity, enable scale, improve security and prevent IP leakage. - What’s new in Perforce Helix IPLM and Helix Core

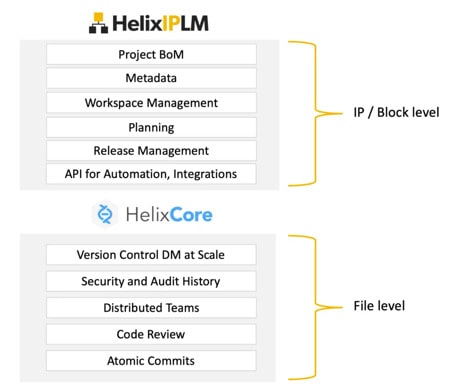

Helix IPLM and Helix Core together provide a unified, scalable IP and design data management platform that tracks IP and its metadata across projects, providing end-to-end traceability and enabling IP reuse. Some tier-one semiconductor firms use Perforce solutions for IP and data management, like NVIDIA, Micron, and Samsung.

Martin walked me through a demonstration of the Helix tools, where Helix Core takes in design files and Helix IPLM performs configuration management operations to enable an IP-level abstraction of these files. Beyond the base design file content, these configurations can also include data sheets, requirements, and meta-data representing the quality and state of the IP in its lifecycle. The resulting database is used to build workspaces, a centralized, corporate IP catalog, and generally organize the IP ecosystem across the enterprise.

This increased level of transparency of the corporate IP assets will increase IP reuse, saving time and money. This approach also provides complete traceability for a project and its constituent IP hierarchy. As a project moves through its lifecycle, each release can be memorialized as an object in the Helix IPLM platform. Important releases can be tagged and easily identified. For example, when an LVS/DRC clean physical implementation is reached for an IP. Releases can also be controlled to implement certain design methodology steps and then further qualified to manage upstream integration, improving IP quality and control throughout the enterprise.

The Bill of Material (BoM) defines the complete SoC IP hierarchy, including its subsystems, PDKs, SW and all of the dependencies. In Helix IPLM, an IP can be any SoC component, including design data, material meta-data, or even the design tool versions being used. Traceability is enforced by Helix IPLM using immutable releases for each asset, including the parent project. Each engineer on a project has a workspace that renders the design files from the BoM hierarchy, and team members are notified as changes are made or bugs issued. Helix IPLM is integrated with EDA vendor flows, Jira for bug tracking, and includes helpful analytics. Git, Subversion, and ClearCase are also supported as alternatives to Helix Core for the data management layer.

Helix IPLM, Helix Core

Part of Martin’s demo showed how an SoC with many IP blocks had an issue with an ADC block. In this scenario, the ADC vendor had changed their IP and then re-ran DRC/LVS, so a new version of the ADC block was released. The team was informed of the new release, reviewed the details, then integrated the new version into their SoC. This tight communication loop improves the design team’s velocity.

With Helix IPLM the user can quickly view all of the library elements as IP blocks in the web interface, or via the command line if preferred, to query the design. In Martin’s demo, Virtuoso was used to make schematic edits on an IP, and meta-data was used to tag this as a work in progress. A new release was made, and checks were run for consistency. To make the release the DRC had to be clean first, and finally the IP version gets updated. Users can view the complete history for any IP to understand what has changed in each release version. Your team gets to enforce its own methodology as a set of rules, scripts, triggers and schema, so that each IP has management governance.

Summary

Designing an SoC is a complex endeavor, requiring scalable data management, IP lifecycle management and an open architecture to co-exist with all popular EDA tool flows. Perforce has been offering an IP Lifecycle Management tool for many years now with Helix IPLM, along with data management through Helix Core. The combination of Helix IPLM and Helix Core have been demonstrated at the major semiconductor design companies, so it’s worth taking a closer look at for your organization.

Related Blogs

- Perforce at the 2024 Design Automation Conference

- LIVE WEBINAR: Automating the Integration Workflow with IP Centric Design

- 2024 Outlook with Adam Olson of Perforce

- The Transformation Model for IP-Centric Design

- Chiplets and IP and the Trust Problem

Comments

There are no comments yet.

You must register or log in to view/post comments.