Hardware emulation arose as a necessity out of the needs of the eighties. By the mid-1980s, semiconductor designs had outgrown the practical limits of gate-level simulation. Gate-level simulation delivered accuracy, but at glacial pace; silicon prototypes performed at real-speed but arrived far too late. The industry needed… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read MoreA Different Angle on Co-Simulation for Systems

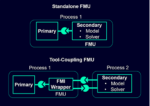

Co-simulation, two or more simulations running concurrently in some manner, is not a new idea. I have written before about multiphysics systems able to model thermal, stress, CFD and other factors simultaneously. I just read a white paper from Siemens based on a different method, using an open standard called the Functional Mockup… Read More

Synopsys and TSMC Deepen AI Design Alliance: What It Means

A recent announcement from Synopsys signals a meaningful escalation in the race to build next-generation AI hardware. The expanded collaboration between Synopsys and TSMC brings together silicon-proven IP, AI-driven design tools, and cutting-edge manufacturing processes in a tightly integrated effort to accelerate high-performance… Read More

Siemens U2U 3D IC Design and Verification Panel

Given the success of the event in Silicon Valley last week, I would expect the Siemens U2U event in Munich to be even bigger. In my experience this has been the best user driven event in 2026 with the deepest customer content. EDA has always been a customer driven industry and it is good to see us recognize that from time to time. Kalar … Read More

Connecting the Dots: Why RISC-V System Design Is Entering a New Era

At the recent RISC-V Now event hosted by Andes, the discussion underscored the fact that RISC-V is no longer just about instruction set architecture advantages or customizable cores. The real focus has moved up the stack to system-level design. This is where connectivity, integration, and security define whether an innovation… Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering Platform

The semiconductor industry is entering a new phase of complexity. Advanced nodes, heterogeneous integration, and AI-driven design workflows are placing unprecedented demands on engineering teams. While much of the focus remains on tools and methodologies, an equally critical constraint is emerging beneath the surface:… Read More

CEO Interview with Geoffrey Rodgers of Chameleon Semiconductor

Geoffrey Rodgers spent most of his career at the intersection of semiconductor technology and go-to-market execution, with a focus on scaling businesses and bringing complex solutions to market. He previously led the Analog Go-To-Market motion at Synopsys following the acquisition of Analog Design Automation and held leadership… Read More

Bronco AI Webinar: Full-Chip SoC Debug in 15 Minutes

A single bug on a full-chip SoC can pull engineers off roadmap work for days or even weeks. It involves massive waveforms, thousands of files of RTL and UVM, and dense specs that aren’t always perfect. Finding these bugs have always been a matter of engineer-hours and how well knowledge diffuses through the organization.

Bronco … Read More

IPLM: Future Forward Webinar May 19th

Step into the future of innovation with the IPLM: Future Forward Webinar—a dynamic, insight-packed event designed for professionals who are ready to rethink how ideas evolve into impact. In a rapidly shifting digital landscape, staying ahead means more than keeping up—it means anticipating change, embracing transformation,… Read More

Podcast EP344: An Overview of the Upcoming Sensors Converge Event with David Drain

Daniel is joined by David Drain, show director for Questex’s Sensors Converge and Broadband Nation Expo, where he leads strategy, content, and industry engagement for two of the company’s flagship technology events. Prior to joining Questex, David spent more than 15 years with Networld Media Group, most recently as senior vice… Read More

Solving the EDA tool fragmentation crisis