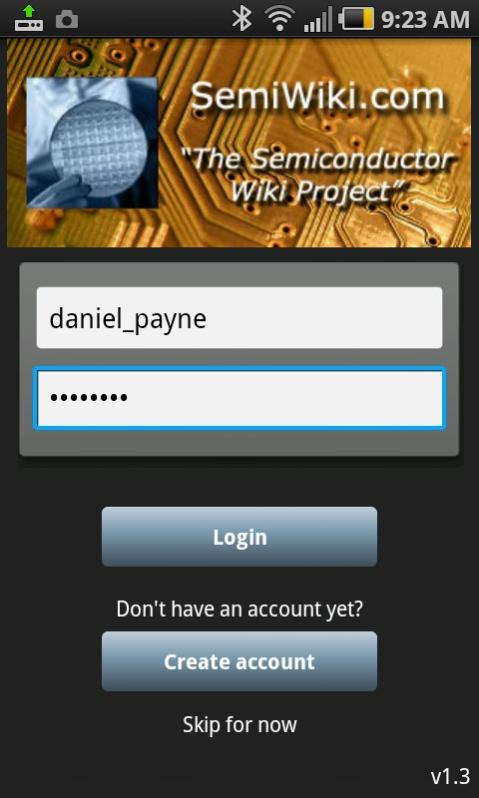

This morning I got to try out the new Android app for SemiWiki, so this is something that you will benefit from as you’re on the go with an Android phone and want to stay up to date. It’s an intuitive app, so you’ll be up and running within minutes. My first step was to visit the Play Store, search for the app using “Semiwiki”, install it and login: Continue reading “SemiWiki on Android”

SemiWiki Releases Mobile Apps!

In response to the growing mobile audience and increasing cost of data plans, SemiWiki has uploaded Android and Apple IOs applications. The SemiWiki mobile apps are available to you at no cost and are advertisement free. The Android app is available TODAY but the IOs app is still PENDING Apple approval (up to 60 days) versus Google Android (24 hours or less). Why? Because Apple individually reviews the apps and Google uses crowd sourcing (user reviews) to track app quality. As a result, I will not order my iPhone5 until the SemiWiki IOs app is approved. Take that Apple!

*** Update: The SemiWiki Apple app is up! And I purchased my iPhone5 as stated. Very nice device! It will do well!

Additionally, not only does Apple charge $99 PER YEAR to have an app in the Apple Store (versus the one time Android fee of $28 from Google), Apple requires you to have a MAC with the new OS to validate your app. So I now own a MAC Air which is a very nice laptop by the way but one I do not really need otherwise. Maybe this is one reason why Android is catching Apple?

According to Daniel Payne’s blog: “EDA Industry Talks about Smart Phones and Tablets, Yet Their Own Web Sites are Not Mobile-friendly“, SemiWiki is now the first EDA media site with a mobile app. Lets hope we start a trend here!

SemiWiki Q2 2012 analytics can be found HERE. To expand on that here are some of the mobile analytics:

Q2 2012 SemiWiki numbers:

Unique Visitors: 85,012

Pageviews: 506,316

15.9% of the visits were from mobile devices:

[LIST=1]

By Device:

[LIST=1]

Google Analytics also sorts by service provider, operating system, input device, screen resolution, demographics, and behavior. Can you imagine what other types of tracking information Apple, Google, and your service provider has on you? Would you trust Samsung with all of your personal information? Let’s just agree that nothing we do on our mobile devices is private.

My son Ryan and I cannot review our own apps since it would be like my wife asking me if her butt looks big in a new outfit that is not returnable. So I have asked Daniel Payne, our resident Android user, to review the SemiWiki app. As soon as the Apple app is up I will ask Paul McLellan, our resident Apple user, to review it. Please download the Android app if you can and let us know how you like it. It is Version 1.3 and we definitely have some more work to do so be kind if you do a review on the Android site.

Speaking of reviews, no sooner than we uploaded the apps we got this email to which we will definitely not respond to, but it certainly makes you wonder:

—————————- Original Message —————————-

Subject: Android / iOS reviews offered

From: “sales”

Date: Wed, September 12, 2012 7:39 am

————————————————————————–

Hello Team Semiwiki,

We are reaching out to you to offer our services for android apps/iOS Apps. These services will UNDOUBTEDLY increase your app’s popularity in Google Play store/ iPhone app store.

We offer positive 5 ★★★★★ star review comments from authentic users (no fake , no spam) which will ensure discoverability and reputation for your app.

· Currently we are offering this service at introductory rate of 3 $ per review.

· We can meet upto 100s of review comments for any app.

· No need to pay in advance , we will let you review a sample batch for free.

· Everyone is using this advantage so don’t get left behind , boost your app.

· You can provide exact comments accentuating features of your app.

Please feel free to reach out to us by replying to this email , we look forward to working with you and starting a symbiotic professional relationship.

All payments to be done via Paypal.

-Regard

Team eDigiMark

Also see: SemiWiki on Androidand SemiWiki on iPhone

ARM, Intel, Apple: It’s Mobile Week

As Dan wrote here, we got invited by Intel to IDF and by ARM to a cheeky little party that they organized the day before. I asked ARM if they were announcing anything and they said basically that it would be foolish to make any announcement the week of their biggest competitors big show. Well, that wasn’t a rule that Apple felt like sticking too, announcing the iPhone 5 in the middle of IDF. Not that Apple and Intel are really direct competitors.

One thing that surprised me was how small the exhibition was at IDF. If you took away all the many Intel booths (and McAffee, WindRiver and other Intel subsidiaries) there is not much there. And quite a bit of it is pretty tangential. Cadence and Synopsys both had a couple of people standing around looking bored. I mean who would go to IDF to meet Cadence, for instance?

Obviously in its main microprocessor business, Intel is very strong, with a weak AMD the only competition. They announced some new lower powered processors. But that is a business that is no longer growing as fast as it did. Intel still seems to be very weak in mobile. I asked ARM if they knew of Intel Atom-based design wins and they said there were a handful, but nothing that seemed to indicate any major shift.

ARM had a lot of phones from Chinese manufacturers like Lenovo that have a price point of $75. They are obviously not as full-featured as the iPhone (which has a price point unsubsidized of more like $650, almost ten times as high). They had touch screens and apps and generally looked pretty good. One of Apple’s weaknesses is that it hasn’t yet come out with an iPhone nano at a much lower price point. Not many people in China, India, Africa are going to buy a $600 phone.

However, in Q4 I’m pretty sure that lots of people in America and Europe (and even some in China) will be buying the new iPhone 5. The 4G LTE modem really does make a big difference. My iPad3 has it already, and downloading email or surfing the web is very noticeably faster than on my iPhone which only has 3G. And I’m on AT&T so actually it is more like 3.5G I’m comparing it to, since AT&T has faster data than Verizon anyway. Oh, and if you are on Sprint or Verizon, which use CDMA, you still won’t be able to access the web and make a call simultaneously like you can on AT&T. The iPhone 5 does not contain a second antenna to access LTE (data) and CDMA (voice) at the same time. I don’t think it is that big of a deal, I’m not sure I’ve ever done it even though I can.

Chip-Package-System Webinar

Aveek Sarkar presented a webinar on chip-package-system (CPS) earlier this summer. One of the big challenges with low-power electronic systems is that the performance, power and price goals are mutually conflicting. It’s like the old joke about “pick any 2”. But for a real system all need to be optimized. The key, in fact, is to design everything together so as to avoid high costs that come from over-designing one particular piece, or the failure that results from under-design. Power noise, signal integrity, electromagnetic interference (EMI), thermal: all of these need to be, like Goldilock’s porridge, just right. Under control without being over-designed at high cost.

Designing the chip, package and board separately and then only bringing them together at the end is no longer adequate since there isn’t enough margin to do a reasonable job of optimizing each aspect separately. They need to be co-designed and analyzed together. Otherwise choices that seem reasonable in isolation, such as using a cheap board or cutting back on decoupling capacitors can be disastrous for system performance or reliability.

Chips are obviously very complex and it is not usually feasible to use the actual design during CPS analysis. Instead, a chip power model (CPM) is used. This captures the essential aspects of the chip to enable analysis of the chip inside its package on the board. The webinar also covers aspects of 3D design, including thermal analysis of a die stack.

The webinar provides an overview of system-aware chip design and chip-aware system design methodologies and how they address complex power, signal integrity, thermal and EMI design requirements. The webinar is now available on-demand.

The webinar registration page is here.

Cadence September News: strong IP and VIP focus

There are three articles on the front page, in the September release of Cadence newsletter, all of them are dedicated to either IP (DDR4), VIP (NVM express VIP being used at Samsung) or Martin Lund. You can read Martin’s interview here and/or take a look at what I write about him this summer. This strong focus on IP, and in fact on Interface IP, is pushing me to take a look at the current status in the on-going chess game between cadence and Synopsys, I will keep this for the end of this article.

Let’s start with the DDR4 Memory Controller IP. As previously noticed in Semiwiki, when Denali has been acquired by Cadence, in May 2010, their DDRn Memory Controller was relying on a soft PHY implementation, still proposed, but the major change after the acquisition is the availability of a hard PHY. Let’s listen to Cadence latest announcement: “The Cadence silicon-proven PHY family includes a high-speed implementation of the DDR4 PHY that exceeds the data rates specified in the DDR-2400 draft, meeting the requirements of next-generation computing, networking, cloud infrastructure, and home entertainment devices, while offering interoperability with current DDR3 and DDR3L standards. Also proven in TSMC 28HPM silicon, is a low-power, all-digital mobile PHY implementation that exceeds the data rates called for in both the DDR-1600 and DDR-1866 DDR3 standards and the maximum data rate of the low-power LPDDR2 standard”.

And Marc Greenberg, director of product marketing, SoC Realization Group at Cadence can justifiably be excited by the availability of such an integrated and reliable solution: “We are excited to be the first to offer silicon-proven DDR4 memory controller and PHY IP that will enable our customers to exceed performance and power requirements in their next generation SoCs with reduced risk. Our broad portfolio of leading design IP solutions delivers advanced features, and a unique approach to customization that allow our customers to deliver highly differentiated products while shortening their time-to-market.”

The DDRn IP market is THE fastest growing segment on Interface IP, as we have found in our latest research, you can see it on this graphic, and also the most promising for the next 3 to 5 years. This is very important to notice, as the investment made by Cadence today on DDR4 will generate ROI for the next three years. On this segment of the interface IP market, I would rank Synopsys head to head, with maybe a small advantage to Synopsys for 2011 results, but we can’t know it precisely as Cadence is not releasing this type of revenue.

The next article is based on a success story, where “Samsung turned to Cadence to reach the speed and productivity goals they’d established for SSD validation. Cadence recommended using the Palladium XP simulation-acceleration use model together with Accelerated VIP (AVIP) for PCI Express. Samsung already used Cadence simulation VIP thus simplifying the transition to AVIP.” This story is interesting as it put the focus on three Cadence’ products: PCIe VIP (at the design stage), Palladium XP (simulation-acceleration) and PCIe Accelerated VIP (AVIP). Just to remind us that, if Synopsys has started to attack Cadence on the VIP market with a couple of acquisition during the last 12 months, Cadence is defending the position. I would guess that Samsung is a large customer, don’t you? As a side question, I would be very interested to know who has designed the PCI Express IP. It could have been designed in-house by Samsung…

Obviously, it would have been a strong move in the chess game between Cadence and Synopsys, if Cadence could have also supported the design IP for NVM Express. Denali has been one of the very first to invest in the Nand Flash controller IP development, that is now called NVM controller, as well as one of the actors in the PCIe controller IP segment. Once again, like with the DDRn IP, the PHY IP was missing to form an integrated solution, but this gap has been closed by Cadence, as they have recently announced the support of PCIe Gen-3 PHY in advanced technology nodes, see here. But, as of today, Synopsys is still the clear leader in the PCIe IP segment, even if they had to acquire the PCI Express Gen-3 PHY technology from MoSys, as blogged here some time ago… which could be an indication about how they are comfortable with PHY IP designed internally.

Just a word from Martin Lund, as this is the 3[SUP]rd[/SUP] article in the September newsletter: “Cadence combined our expertise in interface IP, analog/mixed signal technologies, and system verification to offer customers a complete and full-featured NVM Express interface subsystem,” said Martin Lund, senior vice president, Research and Development, SoC Realization Group, Cadence. “Without this subsystem approach, SoC designers would need to source their interface component IP separately and drive integration on their own, often increasing their design risk and overall development time for new SoCs.”

Coming back to the chess game, my personal conviction is that the “Queen” will be the PHY IP, as the company being able to provide an integrated IP solution, PHY and Controller, should be able to run the game. You may prefer to put it this way: the company unable to provide a PHY (supporting the latest standard release like PCIe Gen-3 or MIPI M-PHY) on the most advanced technology node, will most certainly lose the game, on the long term… Finally, so far, the game is slightly changing: after Synopsys incursion in VIP, Cadence has to defend their position (using “communication bullets”), on the Memory Controller IP segment, both companies are now competing head to head, when on the PCI Express IP segment, Synopsys’ dominant position begin to be challenged by Cadence, as they provide a more consistent solution, because integrating the PHY IP, than Denali, only providing the digital part. Guess what? The game is far to be over, and I am anxious to see what will be the next move, so I will look at the M&A news from both companies.

Eric Esteve from IPNEST –

A Brief History of GLOBALFOUNDRIES

In response to changing industry dynamics, AMD announced in October 2008 a new strategy to focus exclusively on the design phase of semiconductor product development. To achieve that strategy, AMD partnered with Advanced Technology Investment Company (ATIC) of Abu Dhabi to create a new joint venture company designed to become the world’s first truly global contract manufacturer of semiconductor products (or “foundry”).

On March 4, 2009, GLOBALFOUNDRIES launched as the new joint venture combining AMD’s leading-edge semiconductor manufacturing capabilities with the long-term financial focus of ATIC, creating a new global semiconductor manufacturing foundry with approximately 3,000 employees and serving AMD as its first customer.

Through the course of 2009, the company announced several new customers and new strategic partnerships, including ARM, ST Microelectronics, Broadcom and Qualcomm. In June of that same year, GLOBALFOUNDRIES broke ground on the Fab 8 campus, the company’s newest 300mm fab in Saratoga County, New York.

In January 2010, the company announced the completion of its merger of operations with Chartered Semiconductor, a global semiconductor foundry company based in Singapore. At the time, Chartered consisted of about 7,000 employees, mostly based at the company’s 6 fabs in Singapore. The addition of Chartered added more than 150 customers to the company’s portfolio, afforded world class production capabilities in both main stream and leading edge technologies and allowed the company to offer a new platform for innovation to drive the current and future generations of semiconductor products for customers around the globe.

In 2011, GLOBALFOUNDRIES continued to add customers and reach significant manufacturing milestones as AMD’s 32nm processor shipments increased by more than 80 percent from the third quarter to the fourth quarter. In fact, GLOBALFOUNDRIES exited 2011 as the only foundry to have shipped in the hundreds of thousands of 32nm High K Metal Gate wafers.

GLOBALFOUNDRIES is a first-of-its-kind global foundry model, leveraging assets from around the world to best meet the needs of the global marketplace. The company is making substantial capital investments to build a truly global footprint, with manufacturing operations spanning three continents for flexible and secure supply. With more than 13,000 people worldwide, and manufacturing centers in Germany, the United States and Singapore, GLOBALFOUNDRIES is delivering advanced technologies to market in high volume and mature yield faster than any other foundry in the world.

This global manufacturing footprint is supported by major facilities for research, development, and design enablement located across the U.S., Europe, and Asia, with offices in Abu Dhabi and corporate offices in Silicon Valley. The collective strength of these operations is unprecedented for a semiconductor foundry and will be unparalleled in the industry

Today, GLOBALFOUNDRIES is wholly owned by ATIC and is the world’s second largest independent semiconductor foundry and is gaining strong momentum in the global semiconductor industry.

Intel Finally Comes Clean on 22nm SoCs!

Ever since Intel announced that they will leverage their advanced process technology leadership into the mobile SoC market I have expressed my doubts. I know how Intel designs their microprocessors, having worked for many of their vendors over the years and having friends at Intel who are actually doing the work. Disclaimer: Intel was one of the first companies to offer me a job out of college and I have been a big fan of their microprocessors since the beginning, but I’m a fabless SoC guy so I’ve had issues with Intel and their Mobile SoC strategy from day one.

The announcement I have been waiting 1+ year for has finally come. At IDF this week Intel finally admitted that making microprocessors and SoCs are not the same and will require very different design and manufacturing practices. The first Intel 22nm SoC (Bay Trail) will come out “sometime next year” which is PR speak for the end of 2013, if they are lucky.

Today Intel is shipping 32nm SoCs which compete against TSMC/Samsung ARM based 28nm SoCs like the one in the new iPhone5. Next year the Intel 22nm Atom SoCs will compete with the TSMC/Samsung ARM based 20nm SoCs. So much for the so called Intel advanced process lead! I don’t know about Samsung but TSMC 20nm SoCs will tape out in Q1 2013 with production Silicon coming in Q4 (my guess). And I’m not talking about one mobile SoC like the Intel Bay Trail. I’m talking about ARM based mobile SoCs from the likes of Samsung, Qualcomm, TI, Broadcom, Marvell, Apple, Huawei, NVIDIA, MediaTek,etc… and a hand full of others from China.

For more details on the 28nm mobile SoCs see:

Smart mobile SoCs: Apple

Smart mobile SoCs: NVIDIA

Smart mobile SoCs: Texas Instruments

Smart mobile SoCs: Samsung

Smart mobile SoCs: China

Intel was nice enough to invite me and Paul McLellan to IDF this week. Even nicer, ARM had an open house a block away the day before. One thing I have to say is that Intel gives the best conference bag swag! The food, drink, and conversation however were much better at the ARM open house, absolutely.

One of my favorite tech writers, Dean Takahashifrom Venture Beat, was at the ARM open house and wrote a much better piece than I can on it so read his here: Arms race? On eve of Intel’s developer event, ARM argues it’s winning the mobile race. There were also reporters from tech gossip sites like The Inquirer but their articles are complete nonsense. Why bother inviting these buffoons? Seriously!

In addition to good food and drink, ARM had new phone and tablet demos with bill of materials (cost) of around $50. That is where the market is going so you have to ask yourself: What is Intel really going to do once they get into the mobile market? Or better yet, will Intel actually make a difference in the mobile market?

We talked to Simon Segers. Simon started at ARM in 2001 as the VP of Engineering and is now EVP and GM of the Processor and IP divisions. Paul and I also spent time with Suk Lee of TSMC, and ARM lead Mobile Strategist James Bruce. Time well spent! I’m sure Intel now regrets their premature and overly aggressive PR campaign against ARM and TSMC but it was certainly fun to watch!

Samsung Invests in Carbon

I’ve talked before about how venture capitalists will no longer invest in EDA companies since the prospect for a huge return just isn’t there any more. By big return I mean an acquisition at hundreds of millions of dollars, like SPC, CCR, Ambit, Cadmos, Simplex. But we all know that chips cannot be designed without software and so the companies that use the tools are having to step up and fund the investment themselves. This is even more the case in the semiconductor equipment industry, where Intel and TSMC have both (or will, I’m not sure how deals are structured) invested huge sums of money in ASML for 18″ wafer and EUV projects. The most recent EDA investment I know of is Intel and Xilinx investing in Oasys.

And today there is another one. Samsung’s VC arm has invested $4M in Carbon and they have entered into a strategic partnership (although the details of what that means have been left murky). Samsung is a customer of Carbon’s virtual platform technology. In fact they are one of the most advanced users of virtual platform technology in the world. Carbon’s existing investors also participated putting in another $1M. Carbon was actually already cash-flow positive but this investment will allow them to accelerate various ramps in engineering and support.

Samsung is now the largest mobile phone vendor, having overtaken Nokia earlier this year. In smartphones almost all the profit goes to Samsung and Apple, with everyone else a long way behind in revenue and even further behind in profit. Of course Samsung participate in many other markets too, but mobile is so big and still growing fast that it is now the biggest market for semiconductors. More memory is sold to go into smartphones than into PCs, a crossover that happened a year or two ago. It is also a market which involves a lot of software and a lot of complex hardware, and very short product cycles, the ideal combination for virtual platforms to really add a lot of value.

Carbon’s has a couple of key technologies that are obviously useful to Samsung, not to mention all their other customers. First, they can automatically create fairly fast but 100% accurate models of any design for which the RTL is available, throwing away details to drive up the performance. They can also make use of fast hand-crafted, but less accurate models. But the really clever technology allows them to switch from fast models to accurate models. So it is possible to boot a system with a fast model and get it to the point of interest, then switch to the accurate model and monitor in great detail exactly what happens. Carbon call this Swap & Play. This really is important since the alternative is to have models that are somewhat fast and somewhat accurate, which turns out to be something that is no good: too slow for the software developers and not accurate enough for the people who need to worry about hardware details.

Is DDR4 a bridge too far?

We’ve gone through two decades where the PC market made the rules for technology. The industry faces a question now: Can a new technology go mainstream without the PC?

By now, you’ve certainly read the news from Cadence on their DDR4 IP for TSMC 28nm. They are claiming a PHY implementation that exceeds the data rates specified for DDR-2400, which means things are blazing fast. What’s not talked about much is how the point-to-point interconnect needed for large memory spaces is going to be handled.

Barring some earth-shattering announcement at IDF, Intel is way far way from DDR4. The nearest thing on their roadmap is Haswell-EX, a server platform for 2014. (Writing this when IDF is just getting underway is tempting fate, kind of like washing my car and then having it immediately rain.) AMD has been massively silent on the subject of DDR4 fitting into their processor roadmap.

Meanwhile, both Samsung and Micron are ramping up 30nm production of DDR4, and Samsung is publically urging Intel to get moving. Both memory suppliers are slightly ahead of the curve, since the DDR4 spec isn’t official just yet. However, JEDEC has scheduled the promised DDR4 workshop for October 30, something they said would approximately coincide with the formal release of the specification. (In other words, it’s ready.)

We also have to factor in that LPDDR3 just hit the ground as a released specification this May, and memory chips implementing it won’t reach the pricing sweet spot for another year. Most phone manufacturers are still using LPDDR2 for that reason. (Again, iPhone 5 announcement this week, rain on my post forecasted.) Tablet types are just starting to pick up LPDDR3, amid talk the first implementations already need more bandwidth.

So, why the push for DDR4, especially in TSMC 28nm? DDR4 is obviously the answer to much higher memory bandwidth for cloud computing and the like. I’m sure there are others out there, but the Micron DDR3 to DDR4 comparison chart was easy to find.

Interest in DDR4 has to be coming from somewhere in the ARM server camp, otherwise Cadence and TSMC wouldn’t be spending time on it. In spite of the power advances, DDR4 is no where near low-power enough to show up in a phone, and there’s no sign of a LPDDR4 specification yet. ARM 64-bit server implementations are just getting rolling, and Applied Micro’s X-Gene has sampled – with DDR3.

The volume driver for DDR4 – if it’s not PCs – is in question. The natural progression of speed that the PC markets have pushed for looks like it is about to run smack into the economics of affordable implementations, and that in turn could make life for the memory manufacturers interesting. (In a related side note, Elpida’s bondholders have come in saying the Micron bid is way too low.) Or, Intel and AMD could jump in and force the issue, betting on adoption farther down their PC supply chains.

DDR4 and IP supporting it in ARM server space could prove to be a turning point for technology investment, an inflection point in the way things have been done and a change from the PC driving. Or, it could end up being a bridge too far, but paving the way for another specification suited for mobile devices.

What are your thoughts on the outlook for DDR4, LPDDR3, an ARM server market, and the overall dynamics of PCs, servers, tablets and phones versus memory technology?

Hogan University: Second Semester

The next event in the Jim Hogan Emerging Companies series (organized by the EDAC Emerging Companies Committee) will be on 17th October at Cadence (I’m guessing in building 5 but I’m sure there will be signs). The specific topic this time will be How to Raise Money and How Not to Spend it. The evening will focus on different funding strategies and, just as important, efficient use of cash.

The participants on the panel will be:

- Jim Hogan

- Amit Gupta, CEO of Solido Design

- Rahul Razdan, CEO of Ocoos

- Atul Sharan, entrepreneur and angel investor

The schedule starts at 6pm with a reception. The panel conversation will start at 7pm and run until around 8pm when the discussion will be opened to questions from the audience.

The event is free but space is limited so you must register here.