Near-field communication (NFC) technology is finally realizing its potential, thanks to the impetus provided by Apple Pay, and it’s becoming evident from the pre-Mobile World Congress (MWC) buzz coming from several makers of chips, smartphones and wearable devices.

Among the companies displaying NFC products at the 2015 MWC in Barcelona is STMicroelectronics, a leading supplier of Secure Element, a special storage block typically built into an NFC controller chip that safeguards vital information like bank account numbers. The other key building block of the contactless access solution is NFC radio for which STMicro is joining hands with ams AG to put together its analog front-end chip featuring NFC booster technology in the turnkey design.

The outcome of this collaboration is a turnkey NFC design solution, which comprises of ams’ boostedNFC chip combined with ST’s system-in-package (SiP), which in turn, contains controller and 32-bit secure microcontroller for Universal Integrated Circuit Card (UICC), embedded Secure Element and microSD-card applications. According to Laurent Degauque, Embedded Security Marketing Director at STMicroelectronics’ Secure MCU Division, the common reference design can be easily integrated into mobile phones, smart watches, wearables, and Internet of Things (IoT) devices.

ST claims that the turnkey NFC design supports all important NFC standards governing card emulation, including ISO14443 type A/B, FeliCa at data rates of up to 424 Kbps, active peer-to-peer bit rates of 212 Kbps and ISO18092 communication at up to 424 Kbps. Moreover, it boasts major certifications, including Common Criteria, EMVCo and GlobalPlatform as well as certifications from Visa, MasterCard, American Express and People’s Bank of China (PBOC).

ams, the Austria-based supplier of analog ICs and sensors, claims that its AS39230 RF chip boosts the signal on the antenna while increasing the signal strength by up to 10 times when compared with conventional passive load modulation (PLM) methods of transmitting a signal from an NFC tag, card or card emulator to an NFC reader. Moreover, ams promises help for space-constrained designs through reduction in the size of the antenna by as much as 20 times, down to 100mm[SUP]2[/SUP] or less, while maintaining the same signal strength.

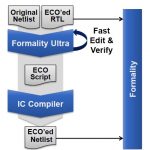

Block diagram of ams’ RF front-end for NFC

ST’s part in the turnkey solution—rolled into an SiP device—is made up of the ST21NFCC controller and the ST33G1M2 Secure Element. ST’s Secure Element is based on the ARM SecurCore SC300 32-bit RISC core and it comes with Common Criteria-certified security features and a large and flexible embedded eFLASH. It boasts Trusted Service Management (TSM) infrastructure compatibility and supports banking and digital access applications through compliance with Global Platform GP2.2 OS and the complete MIFARE portfolio, including MIFARE Classic and MIFARE DESFire.

ST will be exhibiting the new reference design in Hall 7, Stand 7B146 at the Mobile World Congress (MWC) in Barcelona being held on 2-5 March 2015.

2015: The Year of NFC

ST’s partnership with ams for creating an NFC system reference design underscores two crucial facts. First, ST seems to have acknowledged the critical importance of turnkey solutions after the failure of its ST-Ericsson joint venture in mobile baseband business. Chipmakers like MediaTek and Qualcomm provided complete design solutions to a horde of smartphone makers in China and won a very lucrative market.

Second, after going through a number of pain points, the NFC technology finally seems ready for a mass adoption. There had been an industry joke about “The Year of NFC” that perpetually moved to the following year. But now 2015 actually looks like the year of NFC with a number of manufacturers of smartphones and wearable devices lining up to make product announcements at the MWC floor in Barcelona.

The NFC-centric mobile payment ecosystem—mired by security concerns, resistance from mobile operators and a complicated tap-to-pay retail market—had largely been limited to pilot projects. Then, there came Apple Pay, which not only played a significant role in the astounding success of the iPhone 6, but also reinvigorated the sleepy mobile commerce market.

(Image courtesy of Visa)

Apple came up with a simple and effective solution that left mobile operators out of the mobile payment and transaction system. The Cupertino, California–based consumer electronics firm incorporated a Secure Element inside the iPhone 6 so that the Apple Pay service could be provisioned over the air by the issuing bank or the credit card company. Mobile consumers using the Apple Pay app took a picture of the debit or credit card, and after a security check, Secure Element would allow the service to mobile users with the right credentials.

Don Tait, senior analyst at IHS, had told Reuters at the launch of the Apple Pay service back in September 2014 that ST’s strong presence in Secure Element chips would give it a plenty of scalability when NFC takes off. Apparently, NFC’s moment of glory has come, and for ST it’s about time to build a leading NFC position on top of its strong presence in Secure Element components.

STMicro’s ST33G1M2 Secure Element

There is a lot of talk in the technology press about NFC coming to new smartphone models such as Samsung Galaxy S6 and connected wearables like Apple Watch. That could lead to a much bigger market for the NFC silicon—1.64 billion sockets in 2018, according to market research firm IHS.

Majeed Ahmad is the author of Mobile Commerce 2.0: Where Payments, Location and Advertising Converge. The book outlines the major building blocks of the mobile commerce business while providing success and failure stories and profile of key industry players.