Arteris Inc., a network-on-chip (NoC) interconnect IP solution provider, has joined hands with Texas Instruments Inc. to create an ultra-low-power chip that helps Internet of Things (IoT) devices go battery-less with energy harvesting and support coin cell-powered IoT operation for multiple years.

Another low-power MCU parable with energy efficient ARM cores? Well, yes. However, what’s new in this MCU tale is the fact that TI’s new chip supports multiple wireless standards. Another prominent highlight is how TI has implemented Arteris’ FlexNoC interconnect fabric in its SimpleLink ultra-low power wireless MCU portfolio to facilitate the communications part of the IoT device.

The FlexNoC fabric serves as the system-on-chip (SoC) backbone in these low-power MCUs and helps implement IoT wireless communications standards such as Bluetooth low energy, ZigBee, 6LoWPAN and sub-1GHz. TI claims it’s the first SoC product that supports multiple wireless connectivity standards using a single-chip and identical RF design. And the fact that a single die can be used in multiple IoT products allows TI to explore a unique SoC derivatives strategy.

The Dallas, Texas–based chipmaker’s SimpleLink ultra-low-power wireless platform comprises of CC2620 (ZigBee RF4CE), CC2630 (6LoWPAN or ZigBee), CC2640 (Bluetooth low energy), CC2650 (2.4GHz technologies), and CC1310 (sub-1GHz operation) IoT chips.

TI’s CC26xx family of low-power RF devices has integrated an ARM Cortex-M3 MCU, Flash/RAM, analog-to-digital converter (ADC), peripherals, sensor controller and built-in robust security on a single chip. There is a speculation that one of the first CC26xx chips is going into an Oral-B toothbrush for kids.

About FlexNoC Part

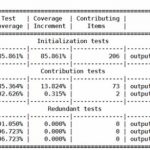

TI has used FlexNoC power disconnect and firewall features to fuse-off select digital I/O controllers and that has enabled various combinations of ZigBee/IEEE 802.15.4, ZigBee RF4CE, Bluetooth low energy, 6LoWPAN, and the proprietary SimpliciTI wireless protocols. As a result, TI was able to produce an entire IoT product lineup with a minimal number of digital logic components.

Moreover, TI brought down the power consumption by employing the inherent low latency performance of zero-latency cycle paths, which were enabled by fully combinatorial logic in FlexNoC interconnect IP. The FlexNoC fabric has also allowed TI to effectively use firmware in meeting the most stringent power and timing requirements.

TI’s IoT chips are an important design win for Arteris that claims that the number one benefit of using the FlexNoC interconnect technology is power management. TI’s General Manager for Wireless Connectivity Solutions Oyvind Birkenes acknowledges the role of FlexNoC’s power management features in creating what he calls the lowest-power IoT communication devices in the world. “FlexNoC allowed us to create a small set of digital logic SoC dies that serve as the brains of more than one hundred different products, each customized for its particular market.”

The implementation of FlexNoC technology inside TI’s wireless MCUs is crucial for Arteris for two reasons. First, IoT is a high-growth market, and an IP socket in a strategic market like IoT is a significant testimonial for Arteris’ network-on-chip technology. Second, it negates the common perception within IC design circles that the NoC interconnect IP products are only used in highly complex SoC designs.

RF and Power Conundrums

According to TI, its SimpleLink family of ultra-low-power MCUs for IoT devices boasts energy footprint that is small enough for a coin cell battery to power a light switch in smart home for 10 years. TI’s wireless MCUs even promise support for battery-less operation of energy harvesting-based sensor nodes.

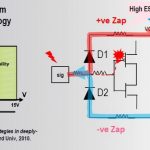

So how were Arteris and TI engineers able to pull off this power management feat? Power management success stories in the wireless domain are typically traced back to the RF part. It’s usually the drain caused by transmit and receive currents inside wireless chips that puts constraints on the battery.

However, a closer look reveals that RF devices like radio transceivers usually don’t contribute much to power consumption within a wireless chip. In fact, it’s small sensors and wireless protocol stacks within an SoC device that mostly add up to power drain. To counter that, for a start, TI’s CC26xx family of IoT chips use two energy efficient MCUs: an ARM Cortex-M3 and a sensor controller.

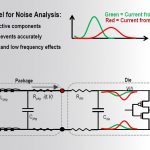

The ARM Cortex-M3 is the main system CPU inside the CC26xx device that consumes less than 3mA while running at the maximum speed of 48MHz. Next up, sensor controller—which comprises of a 16-bit CPU coupled with peripherals like ADC, analog comparators, SPI/I2C and capacitive touch—facilitates interface with external analog or digital sensors autonomously while the rest of the SoC device sleeps.

And that’s only part of the story. TI’s complete chip can stay in standby mode at only 1uA using memory retention and real-time clock (RTC) techniques. According to EEMBC’s ULPBench, it enables the CC26xx platform to offer half the power of other MCUs. Here, TI has put to work many of the FlexNoC power management features to safely disconnect power to individual IP blocks as well as to parts of the on-chip fabric and clock tree.

The designers of portable wireless products can keep the standby currents between the transmissions to minimum and save enough juice in the battery for the active use. For that purpose, in the CC26xx family of IoT chips, TI uses an ultra-low leakage SRAM that can be fully retained while having the RTC running. Meanwhile, CPU is retained in standby mode, which consumes as little power as 1uA. Moreover, in shutdown, the CC26xx can wake up on external I/O events while drawing as little as 150nA.

Take heart-rate monitor, for instance, which needs to run the ADC 10 times per second to capture the heart rate accurately. An ultra-low power CC26xx MCU can let the sensor controller perform all the ADC measurements and wake up the ARM Cortex-M3 every 10[SUP]th[/SUP] ADC sample for optional processing and group RF transmission of this data.

Image credit: Texas Instruments Inc.

Majeed Ahmad is author of books Smartphone: Mobile Revolution at the Crossroads of Communications, Computing and Consumer Electronicsand The Next Web of 50 Billion Devices: Mobile Internet’s Past, Present and Future.