It’s amazing the amount of excitement being ginned up over connected cars. Analyst firms regularly publish estimates of hundreds of millions of connected cars on the road by 2020. It’s enough to make you believe it might happen.

If we even come close to those projections it will be a miracle given the disconnect between the wireless industry and the auto industry. Nowhere is this off-the-hook relationship more apparent than in Europe – where I am this week at Telematics Berlin.

On the cusp of the implementation of the eCall, emergency call, mandate in Europe, car makers and wireless carriers are left to ponder what they have created. Leave it to the wireless carriers of Europe to give the automobile industry the gift of the dormant SIM – a wireless module that is inert until and unless the user has a severe enough crash in their car.

Car companies like PSA, BMW, Renault, Volvo, Volkswagen and Mercedes that have already implemented proprietary eCall systems will find themselves adding a second dedicated and redundant eCall device to accommodate the European Union mandate, according to industry suppliers. This means that the device that was originally conceived to enable a multifunction platform encompassing safety, security and infotainment will be dedicated to a single function necessitating the embedding of multiple telecom modules.

It’s worth noting that in both Brazil and Europe a mandated SIM was “sold” to the industry as a platform for “value-added services” – ie. stuff that car companies could “monetize.” In both instances – Brazil and Europe – the promise has been left unfulfilled. (Brazil’s mandate has been indefinitely delayed while Europe’s mandate appears to be on track for 2018 implementation.)

Should a car equipped with a dormant SIM eCall experience a crash, the dormant SIM module will spring to life and call for help – provided it is within range of a compatible network. Our fingers will be crossed on that point.

The latest European development sure to please smartphone makers along with Apple and Alphabet is the decision by Three, Tesco Mobile and Vodafone to offer inclusive data roaming for smartphone plans. The plans vary – ranging from 2GB up to 12GB of inclusive data roaming. The offer will be a boon to drivers who prefer to use their phones instead of the embedded wireless systems in their vehicles.

According to an Engadget report the deal has been “introduced ahead of new legislation, drawn up by the European Commission, which will scrap EU roaming charges altogether in 2017. A stop-gap measure was introduced last month, limiting the fees that network operators can enforce abroad.”

The problem here is that wireless carriers and regulators generally regard the telecom device built into a car as an M2M or, more importantly, a B2B system. The carrier is treating the car maker and the car as the customer so it is considered wholesale business – not subject to the same rules as retail smartphone roaming regulations.

This means that the removal of roaming limitations for consumer phones will not apply to devices built into cars. It also means that built-in telecom modules are subject to termination by carriers in some parts of the world who prefer to shut those telecom modules off for good if the consumer does not extend the contract beyond the free period.

As a result of these unfriendly policies it is reasonable to conclude that wireless carriers are not overly fond of connected cars – with the possible exception of AT&T and Vodafone (and Orange, Verizon and Telenor). By the same token, car makers are not overly fond of wireless carriers or vehicle connectivity generally. Wireless service for cars is complicated, full of security risks, and expensive. But the onset of the co-called eSIM may change everything.

As demonstrated at the Mobile World Congress with a Samsung Gear smartwatch, the day may soon arrive when consumers can provision the carrier of their choice in their car with the help of a smartphone app. They will also be able to transfer that privilege to a second owner of the car.

http://tinyurl.com/js8ob54 – A New SIM – For a New Generation of Connected Consumer Devices

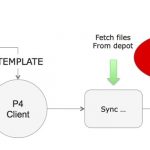

Illustration of carrier provisioning process for Samsung watch with eSIM. – SOURCE: GSMA

The effect of emerging eSIM technology will be to allow the consumer to add their connected car to their existing wireless plan with all that that implies regarding the use of data and roaming. How far off on the horizon is this dream? Maybe not as far off as you think, judging by the presentations and live demo of the provisioning process portrayed in the (above) link.

The eSIM solution opens the door to a carrier-independent world of vehicle connectivity capable of resolving the conflicts and confusion that currently characterize carrier-car maker interactions. If eSIM technology sees rapid and wide adoption, the visions of hundreds of millions of connected cars may indeed be realized – and even sooner than expected.

But lost in all this excitement may be the importance of capturing vehicle diagnostic data and enabling firmware over-the-air updates. The value of the embedded SIM lies in developing a lifetime relationship with the car and the customer and preserving and enhancing the driving experience after the sale.

Until now, car companies have obsessed over the cost of wireless service with little help from the carriers. Multiple efforts are now underway from the Open Mobile Alliance and the International Telecommunications Union to find ways to build strong common bonds between carriers and car makers.

These parties need not and must not be in conflict. The challenges must be overcome as we have seen what will happen in the absence of cooperation – cars will fail and be recalled, carriers and car makers will be blamed, customers will be lost and profitability will suffer.

With the provisioning of a telecom module embedded in a Samsung Gear smartwatch the carriers and car makers were given a vision of what could be. It is time to embrace that vision.

Roger C. Lanctot is Associate Director in the Global Automotive Practice at Strategy Analytics. More details about Strategy Analytics can be found here: https://www.strategyanalytics.com/ac…e#.VuGdXfkrKUk