When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 100X higher performance on common vision processing tasks than the previous generation EV5x! In fact, even if EV6x is part of ARC CPU IP family, this vision processor is a completely new product, defined to address high throughput applications such as ADAS, video surveillance and virtual/augmented reality.

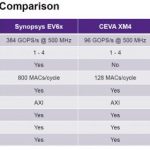

EV6x has heterogeneous multicore architecture including one to four high-performance vision CPU cores. Each vision CPU includes a 32-bit scalar unit and a 512-bit wide vector DSP and can be configured for 8-, 16- or 32-bit operations. In the maximum configuration of four vision CPU cores, the processor delivers up to 620 GOPS/s with full scatter-gather and predication capabilities. From the competitive comparison table below, we can extract the main EV6x differentiators: at 500 MHz, vector DSP delivers 384 GOPS, or 50% more than the closest competitor; CNN performance is even more impressive, with 800 MACs per cycle, when the other two competitors are offering 128 MACs/cycle!

Why does Convolutional Neural Network (CNN) becoming key part of a vision processor? Because CNN is supporting deep learning and this approach outperforms other vision algorithms. Attempting to replicate how the brain sees, CNN recognizes objects directly from pixel images with minimal pre-processing. For vision, CNN can be used to process multiple tasks, like image classification, search for similar images, or object detection, classification and localization. These tasks are supporting automotive ADAS systems, for example, but not only. EV6x vision processor will support surveillance application as well as drones, virtual or augmented reality. CNN is very efficient in face recognition, visual attention and facial expression or gesture recognition.

The CNN engine integrated in the EV6x vision processor not only delivers 6x higher performance than competitive solutions, it also represents the state-of-the-art power efficiency, offering 1000 GOPS per Watt. The CNN engine operates in parallel with Vision CPU, increasing efficiency and throughput. Such performance allows running real-time, high quality image classification, object recognition or semantic segmentation. Last point, this CNN engine is fully programmable to support full range of fixed point CNN graphs, and supports resolution up to 4K.

EV6x vision processor being part of Synopsys DesignWare has been designed for easy integration with any host processor (ARM, Intel, ARC…) in a SoC as the embedded vision processor supports AXI interconnect. Synopsys is used to deliver a complete design environment, offering HAPS FPGA platform for hardware prototyping, reference design and virtual platform, allowing early software development, using EV6x simulation models.

The automotive as well as the surveillance market are very dynamic these days and fast Time-to-Market (TTM) is becoming critical. Synopsys offers reference designs for speed sign or face detection and has built partnership with vendors delivering video surveillance or ADAS application software. The company has made the porting of OpenCV 2.4.9 to RISC scalar core and of OpenVX 1.0.1 standard kernel library, both standard codes being dedicated to embedded vision application.

Availability

The DesignWare EV61, EV62 and EV64 processors are scheduled to be available in October 2016. The MetaWare Development Toolkit and EV SDK Option (which includes the OpenCV library, OpenVX runtime framework and OpenCL C compiler) will be available in June 2016.

Learn more about Synopsys’ Embedded Vision Processors: DesignWare EV6x Processor Family

From Eric Esteve from IPNEST