The rationale behind the Tower Semi acquisition and things to watch out for at Intel’s investor day.

Intel bids for Tower Semi

First I have to quote myself because Tower was an error of omission. In November in a piece that was likely too long for its own good, I mentioned that trailing edge fabs are in a huge position of strength and even called out Tower Semi.

A name that I think is worth looking into, but I don’t really have the bandwidth for at this moment, is Tower Semi. It screams like a strategic asset, and all they’ve been doing for the last 10 years is buying lagging-edge fabs. Keep an eye on that, but for now I still think these aren’t as attractive as just metrology companies in Semicap.

First I think it’s funny because semicap has only gone down since then, and Tower Semi of course got a nearly 50% premium bid. So let’s dive a bit deeper into why Tower Semi is such a strategic asset and why Intel is buying them right now. Let’s start with a brief history of Tower Semi.

Tower Semi – The Fab Partner

Tower Semiconductor’s (formerly TowerJazz) history is a storied one. The beginning of Tower starts in 1993 with National Semiconductor’s divestiture of its Israeli fab in Migdal Haemek, Israel. Tower expanded its Israeli footprint with Fab 2 alongside Fab 1 in 2001.

The real transformational deal that made Tower into who they are today was an all-stock merger with Jazz semiconductor in 2008. Jazz semiconductor actually started as a subsidiary of Conexant and was funded by the Carlyle group. Jazz was taken public by a blank check company (SPAC!) and their fab is the Newport Beach fab.

The next big win was a Panasonic JV that enabled Tower to launch 3 Japanese fabs with Panasonic as the main customer and 49% owner. This JV helped Tower offer 65nm CMOS and 300mm technologies for the first time.

In 2016 they acquired another fab with the purchase of Maxim Integrated’s San Antonio fab. This was a way to offload the Maxim fab to transition to a fab-lite model and helped expand production of 200mm wafers for Tower.

Last but not least is the Agrate Italy fab. Tower Semi partnered with STMicroelectronics in 2021 to share the cleanroom of this fab. Tower has 1/3rd of the cleanroom and helps ramp the cleanroom to higher utilization faster.

A simplified graphic of their fab footprint is below.

Notice the types of deals Tower pursues, they are primarily JVs. Tower is the fab partner for many larger IDMs, and by acquiring Tower, Intel now has a new customer opportunity given the tight integration of JVs. Panasonic is Tower’s largest customer at ~25% of revenue, but there are 5 additional customers that account for 4-11% of sales. Then a long tail after that. The tail in particular is Intel’s opportunity.

I want to last talk about some of the niche products Tower has. They seem to be the leading Silicon Germanium (SiGe) manufacturer in the world, a specialty process that is useful for RF (radio frequency) front end. Tower is also a leader in silicon photonics fabrication.

In Tower’s own words their biggest drivers are RF CMOS, industrial sensors, RF mobile, and RF Infrastructure (datacom photonics). In particular, some amount of power ICs fabbing capability for Intel makes sense, RF CMOS likely is just nice to have, and RF infrastructure aligns almost directly with Intel’s future ambitions.

Notice the technology, the majority of their capacity is at the 200mm wafer sizing. While these fabs are “specialty” products, their 6-inch and 8-inch power capacity is not particularly special. I would say there is a good mix of leading specialties like the 300mm CMOS and SiGe (Silicon-Germanium), but the 150mm and 200mm power is relatively commoditized capacity. So now let’s discuss why Tower is a good fit for Intel.

Intel Foundry Service’s Jump Start

A reminder that Intel is not letting go of its Fab, but rather amplifying its fab capabilities in its “IDM 2.0” strategy. This is a renewed commitment to fabbing Intel’s own products, as well as opening up their fab and PDK (Process Design Kit) to other companies and customers. The thought here is that they can further leverage their large fab footprint and offer highly desired leading-edge foundry services to their customers in a time when companies desperately want more leading-edge capabilities. But where does Tower fit into that given their mostly lagging edge capacity?

I think Tower completes the fab footprint in a holistic sense. Imagine you want to fab something completely custom at Intel. It’s a whole unit of data center compute not just a CPU, with connected custom fabric, some silicon photonics, and of course, its power-hungry (PMICs).

In the current Intel world you could just get the leading edge chip and packaging, but not the rest of the silicon, photonics, or power IC that composes a total system. Imagine trying to buy a car and only being sold the engine and the ability to attach the engine to a car (packaging), that is the current scope of Intel Foundry Service (IFS).

Tower expands this. Now we have a full-service shop. And it’s no surprise actually if you look at their peer Taiwan Semiconductor, which is known for its leading-edge logic. But a closer look shows that 37% of TSMC’s revenue consists of geometries larger than 28nm. So in the case of TSMC, you can go to them and get the full solution. If IFS is to compete for head to head, they need Tower to complete their full solution.

This was discussed on their M&A call:

This combination of leading edge and specialty technologies will position us as a truly global end-to-end foundry. When we launched IFS last March, our customers were overwhelmingly excited to work with us. One of the things that consistently asked me was to add specialty and mature nodes to our portfolio. With Tower, we can honor that request and more broadly serve key market segments.

You can’t have a compelling IFS without making it full service. But more than that I think one of the biggest benefits is adding a new culture that is actually customer-centric. Some of the past critiques of Intel’s foundry plans were inflexibility and non-standard workflows.

Working with Intel in the past was like showing up at someone else’s garage and being forced to use their wacky tools and blueprints not being given much insight into how things were made. Tower has standard workflows and a more customer-centric fab culture, and this could be a huge kickstart to creating a standard workflow at IFS.

Yes. And while some of this is premature to talk about it too much detail, given the regulatory process, my expectation is that we will fully merge IFS and Tower into a single foundry business for Intel going forward. And part of the value and the synergy of the acquisition as the question suggest, is to fully benefit from that decades of experience that Tower brings and how to run a global foundry customer-centric business for our customers for the future. So overall, we’ll lay out more of that integration strategy as we get to the time of deal closure. But this will become one foundry business that will be the full integration of IFS today with Tower today.

So assuming IFS and Tower are all one unit, I am now warming up to a foundry spin. It was directly in opposition to what Pat Gelsinger has said before, but let’s examine it from the perspective of Gelsinger’s history and what he knows, aka the Dell corporate structure.

Intel Might Spin Foundry Now

I have followed the Dell complex (for lack of better words) at a surface level for a few years now. Michael Dell, the founder of the PC giant Dell, took Dell private in an audacious LBO with Silverlake. Pat Gelsinger worked at one of the subsidiaries at the time, and the subsequent corporate structure is likely familiar to Pat. While I don’t think Pat Gelsinger is going to take the Dell route it’s good to look at the corporate patterns and behaviors he knows best.

For context, Pat Gelsinger joined EMC as COO in 2009 and has watched the entire Dell structure emerge. This included the EMC collapse into Dell and the spinout of VMWare back to public markets. I’m sure he’s well versed in the logic of spin-offs and tracking stocks that were used at Dell. In fact, you can argue that the partial spin of Mobileye looks a lot like something Dell did with Vmware originally. I now think that this is what will happen in some capacity with Intel Foundry Services.

I don’t think this happens immediately because of the huge capital requirements of IFS, but I do think that post Mobileye spin, the promise of an IFS will be a carrot held over investors’ heads. IFS will be a completely separate unit, and now it has a history of financials and some kind of internal structure that it will inherit from Tower. It’s primed to spin.

I think that it will be mentioned as a “strategic option given market conditions” and broken out segment-wise. This will force investors to start to consider Intel as a SOTP valuation first and foremost. I know that this seems like a headache but Pat’s primary focus is likely on the technology side of things, and it’s easy to slip into what he knows corporate structure-wise. Especially when it enriched the Dell CEO so much. And having that potential option is going to be a valuable card to play in my opinion.

Intel would become a quasi holding company in this scenario, with partial stakes in faster-growing businesses (MBLY, IFS) while its core fabless business itself would be likely a slower growth entity that gets to benefit from its partial stakes in these tracking stocks. This sounds frankly the future of Intel. Now let’s move on to what to expect from Investor day.

Subscribe to Fabricated Knowledge

Intel’s Investor Day

I am for one excited for Investor day. Here are a few of the things I expect:

Resegments and new long term models for each segment

An absolute kitchen sinking of FY22 numbers

Guide up revenue marginally

Gross margins sub 52%

Guide down earnings

Some kind of FCF guide

An aggressive Capex plan, possibly matching TSMC

Mobileye discussion, and the hint of spinning IFS eventually

Progress reports on their catch up plan

They will promise performance parity in 2023

I’m almost certain I will be surprised by something they have. I expect some kind of product announcement, and in particular, I would love to hear more about their DPU.

I wanted to make a bingo sheet but didn’t have exactly enough time. I’ll be watching and live-tweeting the whole event on @_fabknowledge_

I will of course be drinking every time Pat says something horny, e.g. “puberty” at Intel, or “lusts” for fabs. But I’m excited about a good show and have to say, I am the most bullish I have been on Intel in a while. I think there is a chance they can really surprise us, and while I know that the FY22 numbers are about to get brought down, I believe that most investors already know this. Everyone knows that, and in recent days every expected miss has been reversed. I expect that to happen at Intel.

Also Read:

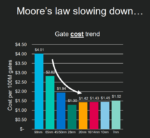

The Rising Tide of Semiconductor Cost

How France’s Largest Semiconductor Company Got Stolen in Plain Sight