Insights into the Semiconductor Industry and the Semiconductor Supply Chain

I am not an expert in geopolitical issues, but lately, my research has begun to worry me. As I was preparing to be interviewed for Chinese media, I was in my “Chinese Zone”, adapting to what is palatable to a Chinese audience. Maybe my mode provoked the thought:

Who would benefit from eradicating the entire Taiwanese Semiconductor industry?

What if China is not deterred by potentially mined TSMC factories and ASML kill switches? What if the reunification plan is based on eradicating the TSMC factories and the Semiconductor supply chain in Taiwan and beyond?

For the first time, I can see the outline of a military invasion plan that can significantly benefit China, but the implications are scary. While I have no indications that this is actually about to happen, this is within the “Strong Man” thinking. This article describes that scenario and its implications.

The Three Reunifications Scenario

My upbringing in a small, peaceful country devoid of geopolitical ambitions during the Cold War has shaped my understanding of these issues. Living less than 200km from the Warsaw Pact border, I witnessed the system before and after the wall fell. The system didn’t crumble with the wall. It retreated to Russia, reorganising under the guise of democracy and economic reform. I experienced this firsthand during my extensive travels in Russia, not just the “civilised” parts.’

I’m not writing this in my mother tongue and only a few comprehend what it means to be Danish. As a small nation, we are not imperial and don’t need nationalism, we need cooperation with other countries, primarily in the coal union that brought peace to the parts of Europe that formed the EU.

Although not an expert, I feel qualified to give my view of the geopolitical situation, and I have no problem with others disagreeing with my assessment.

The background

After the fall of the Soviet Union, a new US-led, rules-based world order began. It was based on alliances and corporations and supported civil rights, free speech, and democracy. It was the birth of globalism.

The Semiconductor supply chain evolved and grew in locations where it made the most sense, and nobody interjected or tried to dictate this development. Most US semiconductor companies were happy to eliminate the hassle of making chips that could be made better and cheaper in Asia.

The world is moving from the rule of law to the law of rulers

That order is now breaking down. The US standings in the world have deteriorated due to long wars with little plans for the aftermath and the increasing division of the US society. Trust in elections and institutions is at an all-time low. The more the US tries to dictate the world order, the less it succeeds, as the USA has become unpredictable to the rest of the world. The outcome of a US election can now create two very different scenarios for the world order, and the election itself will be disrupted no matter what. A few votes in a swing state, a Florida judge or a Supreme Court decision can decide the election.

World order and Strong men

The breakdown of the rules-based world order got plenty of help from the outside. Democracy and free speech are not Strong Men’s favourite dishes. It goes against the dictator’s playbook, which has three chapters:

- The Enemy Within – I alone can fix it

- Prosperity – I am the system, and it is good for you

- The external Enemy, I am the only one to protect you.

The enemy within is the tool to gain power. The breakdown of trust in politicians, institutions and society in general. It culminates when political opponents are hated more than external “enemies”.

For many years, Putin had a “deal” with the Russians that if they stayed out of politics, he would make them more prosperous, and he did. From the late nineties and 15 years on, the standard of living increased dramatically. But this was built on an organised cleptocracy that stole from the people and eventually ran out of steam.

Enter the external enemy. It is time to make Russia great again, first by covert little green men operations and later the full-scale invasion of Ukraine. As this did not go well, the enemy was changed from Ukraine to the West. “We are fighting the collective forces of the West.”

The overarching objective of a Strong Man is to keep power after securing it. Self-perseverance is key. If only a few per cent of the population starts to protest, you are in trouble. Stability is your friend.

Where Putin is deep in 3 and has transformed the entire Russian society into a war economy, President Xi is likely at the end of 2. The massive infrastructure and real estate investments are starting to look hollow, and economic growth is slowing. It’s time to make China great again.

Everyone is aware of China’s increasing military ambitions. Its claim to atolls in the South China Sea and naval conflicts with all its neighbours point to a new geopolitical reality.

The no-limits partnership between Russia and China and the latest treaty between North Korea and Russia opens up the possibility of a potentially devastating conflict to make Russia, Korea and China reunified and great again.

He who controls the present controls the past.

He who controls the past controls the future.

George Orwell, 1984

A vital element of the Strong Man’s storyline is the past. Everything was better, and we were stronger and a larger unified nation. If you have the ultimate power, you can make insurrections, nuclear accidents, and squares disappear. The past is no stranger to a strong man.

Ruler of the past (what is left)

While Western politicians come and go, China and Xi understand how to play the long game. The semiconductor industry has been a focus area for decades, while Western corporations cannot see beyond the quarterly boundary.

I slept relatively well at night, believing China couldn’t conquer Taiwan and preserve the Semiconductor industry. A scenario without winners that would set the world back 15 years or more.

I realised that a destructive reset could become a long-term advantage in a long game. If Xi were willing to turn back the clock 15 years, China could emerge as the winner of the past, of whatever was left.

Prelude

The Three Reunifications Scenario might not be the original plan, but it could have developed due to Russia’s invasion of Ukraine. This is the prelude that China has observed the overwhelming Russian war machine being degraded by drones and precision weapons from the West. It is unlikely that other invasions will differ, so any attempt to conserve part of the conquered industry is an illusion. Destruction is inevitable.

Diversion

Surprisingly, China has not commented much on the Russis-North Korea Defense pact. Why is China not uncomfortable with Little Rocket Man getting better rockets? Maybe because the next part of the plan is a North Korean attack on South Korea. This would further stretch Western military resources and deplete the already dwindling military resources. China could lean back and say: Not our problem. While it is unlikely that North Korea can conquer South Korea, it can destroy a lot of the South Korean Industry.

Finale

The West’s involvement in two wars of attrition forms the basis for an invasion of Taiwan. There is a limit to how many conflicts the US military and its Western allies can be in simultaneously. That might allow China to invade Taiwan without too much or any direct involvement from outside forces. With part of the US political establishment becoming more isolationistic, the West would likely be unable to handle three military flashpoints at a time.

Although I knew the tensions between Ukrainians and Russians first-hand, I was convinced Russia would not invade – I could not see the logic (maybe strongmen don’t use logic). I hope I am also wrong about the Three Reunifications Scenario. Unfortunately, I can see the logic in it from a Chinese perspective.

The current Manufacturing View:

Although not all companies have all manufacturing in their legal jurisdiction, it is the exception rather than the rule.

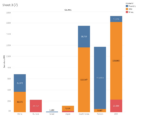

The distribution of semiconductor Property, Plant, and Equipment (PPE) gives a good overview of the manufacturing capacity from a geographic perspective. Chinese privately (state) owned companies are adding an estimated 35B$. These companies specialise in Memory, Micro, CPU, and mobile semiconductors.

While PPE includes other assets, these are very small for a Semiconductor Manufacturing Company. The Fabs and equipment dominate PPE. It can also be argued that PPE is higher per dollar of revenue in the US than in China and that advanced manufacturing takes more PPE value. These are all fair arguments to consider. Still, PPE is a much more solid number than most in the industry.

We divide manufacturing capacity into three categories:

- Integrated Device Manufacturing (IDM)

- Semiconductor Foundry

- Mixed Manufacturing

Traditionally, all semiconductor companies were IDMs that manufactured and sold branded products. With the emergence of TSMC, companies could choose to outsource manufacturing and go fabless. Some companies have chosen the mixed model and retained some manufacturing capacity while outsourcing the rest.

The USA is still dominant despite some US capacity in other jurisdictions, so the physical location is elsewhere. Intel has Fabs in Ireland, Israel, and Malaysia, but most of its capacity is in the US. From a PPE perspective, Intel is not getting as much value from its manufacturing assets as TSMC is. This is a function of Intel making subpar manufacturing decisions, excluding Deep UV equipment. Despite these discrepancies, we still believe that a PPE analysis is solid and a source of good insights.

The PPE analysis shows that most of the chip manufacturing capacity is concentrated around the East China Sea, and 50% is in potential “Reunification” zones.

China’s 12% share of global PPE might sound low, but it is growing incredibly. Despite the US lead embargo, China still buys nearly half of the Western semiconductor tools sold, amounting to a roughly 31B$ annual run rate plus an additional 4B$ of Chinese tools. The embargo and Chips Act only accelerated this development.

The total Chinese PPE is projected to pass 100B$ within a year with these numbers. A near 50% growth will give China an estimated 18% global capacity.

If the semiconductor manufacturing capacity of South Korea and Taiwan is excluded, China will have a third of the global capacity by the end of the year. For every year that passes, China will gain more capacity than even the US.

With the exclusion, the total capacity, based on PPE, will decline from 550B$ to 300B$

Revenue versus Capacity

As global semiconductor revenue has been an average of $550B over the last couple of years, and the combined PPE is also around 550B$, it can be assumed that 1$ of PPE can generate 1$ of annual revenue. This might be too crude for accounts, but it can be used for this scenario.

Excluding Taiwanese and South Korean manufacturing, the world would be set back 15 years from a manufacturing standpoint. China would command 1/3rd of the capacity at the end of this year. This share would grow significantly every year any military action is delayed. Time is on China’s side.

How this will be devastating to the US

Based on the PPE analysis, the US would be a significant winner in the Three Reunifications Scenario, but there are some complications. The first is that the US capacity is concentrated in one company, Intel, which is not in the best of shapes. As with the other US semiconductor companies, Intel’s business heavily depends on the supply chain in Asia, especially the high-tech supply chain of Taiwan, Korea and Japan.

The destruction of the Semiconductor Supply Chain

The destruction will not only impact semiconductor manufacturing but also the semiconductor supply chain. A Korean conflict could impact US manufacturing positively, while the supply chain implications are minimal. A Taiwanese conflict, however, would be negative for the US. For the large US fabless companies it would be catastrophic and US rely a lot on the high tech Taiwanese supply chain.

The smaller and more sheltered Japanese and European Semiconductor industries are more sheltered and self-sufficient from a supply chain perspective and would likely fare better than the US.

Excluding Taiwanese and South Korean manufacturing, the world would be set back 15 years from a manufacturing standpoint. China would command 1/3rd of the capacity at the end of this year. This share would grow significantly every year any military action is delayed. Time is on China’s side.

How this will be devastating to the US

Based on the PPE analysis, the US would be a significant winner in the Three Reunifications Scenario, but there are some complications. The first is that the US capacity is concentrated in one company, Intel, which is not in the best of shapes. As with the other US semiconductor companies, Intel’s business heavily depends on the supply chain in Asia, especially the high-tech supply chain of Taiwan, Korea and Japan.

The destruction of the Semiconductor Supply Chain

The destruction will not only impact semiconductor manufacturing but also the semiconductor supply chain. A Korean conflict could impact US manufacturing positively, while the supply chain implications are minimal. A Taiwanese conflict, however, would be negative for the US. For the large US fabless companies it would be catastrophic and US rely a lot on the high tech Taiwanese supply chain.

The smaller and more sheltered Japanese and European Semiconductor industries are more sheltered and self-sufficient from a supply chain perspective and would likely fare better than the US.

China, however, would emerge as the winner. The Chinese semiconductor industry follows the deep tradition of locally building the entire supply chain. From raw goods to finished products.

As semiconductor materials manufacturing is not as PPE intensive as semiconductor manufacturing, it is more relevant to look at revenue:

According to SEMI research, in 2023, more than 35% of all Semiconductor materials outside Taiwan and South Korea will be in China.

Taking out most of the leading-edge manufacturing and supply chain would leave the Chinese semiconductor industry in the sweet spot, ready to serve the world. As the Chinese are experts in value chains, they are not likely to sell their semiconductors directly to the West, but they will be more than happy to sell them wrapped in products. Your next electronic products—phones, PCs, and Cars—might be Chinese, but you must wait until AI is back on the agenda, as the Semiconductor clock has reversed a few years.

It would serve many of Xi’s goals, including reunification, however ugly. An external enemy could be potentially humiliated by non-intervention. China is emerging as the number one country in semiconductors (based on mature nodes turned leading edge), with most of the high-tech manufacturing in the world.

As I started by saying: Fortunately, this is just a scenario….

Also Read:

Blank Wafer Suppliers are not Totally Blank