There are a large number of challenges at 20nm that didn’t exist at 45nm or even 32nm.

There are a large number of challenges at 20nm that didn’t exist at 45nm or even 32nm.

The biggest issues are in the lithography area. Until now it has been possible to make a reticle using advanced reticle enhacement technology (RET) decoration and have it print. Amazing when you think that at 45nm we are making 45nm features using 193nm light. A mask is a sort of specialized diffraction grating. But at 20nm we need to go to double patterning whereby only half the polygons on a given layer can be one a reticle and a second reticle is needed to carry the others. Of course the rules for which polygons go on which reticle are not comprehensible to designers directly. It is also likely that we are moving towards restricted design rules, where instead of having minimum spacing rules we have rules that restrict spacing to a handful of values. We’ve pretty much been doing that for contact and via layers for years but now it will affect everything. This explosion of design rules means that the design rules themselves are pretty much opaque to the designers who have to follow them and tight integration of design rule checking, RET decoration, reticle assignment and so on must be tightly integrated into both automated tools (such as place and route) and more manual tools (such as layout editors).

Another theme that goes through many blog entries here is that variation is becoming more and more extreme. The variance gets so large that it is not possible to simply guard band it or else you’ll find you’ve built a very expensive fab for minimal improvement in performance. Variation needs to be analyzed more systematically than that.

These two aspects are major challenges. Of course we have all the old challenges that designs get larger and larger moving from node to node requiring more and more productive tools and better databases. Not to mention timing closure, meeting power budgets, analysis of noise in the chip-package and board, maybe 3D TSV designs. Manufacturing test. The list goes on.

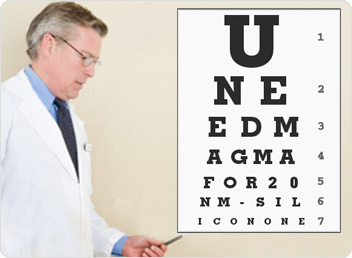

To get a clear vision of what success will require, view Magma’s webinar on 20nm SoC design here.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center