The announcement today that Intel will be a Foundry for Altera at 14nm is a significant turning point for the Semiconductor Industry and Intel’s Foundry fortunes of which the full ramifications are not likely to be understood by analysts. As a long time follower of Intel and a former co-founder of an FPGA startup (Cswitch), it has… Read More

Tag: xilinx

Zynq out of the box, in FPGA-based prototyping

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More

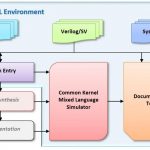

An FPGA Design Flow with Aldec Tools

I’ve used FPGA vendor-supplied tools from both Xilinxand Lattice Semibefore, so I wanted to see what EDA tools Aldec has to offer for FPGA design. I read the Aldecwhite paper, Corporate Standardization of FPGA Design Flow, and summarize what I found.… Read More

What I Learned About FPGA-based Prototyping

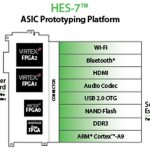

Today I attended an Aldec webinar about ASIC and SoC prototyping using the new HES-7 Board. This prototyping board is based on the latest Virtex-7 FPGA chips from Xilinx.

You can view the recorded webinar here, which takes about 30 minutes (should be available in a few days). I first blogged about the HES-7 two months ago, ASIC Prototyping… Read More

The logic of trusting FPGAs through DO-254

Any doubters of the importance of FPGA technology to the defense/aerospace industry should consider this: each Airbus A380 has over 1000 Microsemi FPGAs on board. That is a staggering figure, especially considering the FAA doesn’t trust FPGAs, or the code that goes into them.… Read More

Xilinx Programmable Packet Processor

At the Linley conference last week I ran into Gordon Brebner of Xilinx. He and I go a long way back. We had adjacent offices in Edinburgh University Computer Science Department back when we were doing our PhDs and conspiring to network the department’s Vax into the university network over a two-week vacation. We managed to … Read More

12m FPGA prototyping sans partitioning

FPGA-based prototyping brings SoC designers the possibility of a high-fidelity model running at near real-world speeds – at least until the RTL design gets too big, when partitioning creeps into the process and starts affecting the hoped-for results.

The average ASIC or ASSP today is on the order of 8 to 10M gates, and that includes… Read More

Altera’s Real Impact with ARM based SOC FPGAs

At the annual Linley Processor Conference this past week a number of chip vendors proposed a raft of new networking solutions directed at solving today’s bandwidth issues. Perhaps the overall highlight of the conference was the recognition by Keynote Speaker Linley Gwennap of the shift that is taking place towards ARM based solutions.… Read More

A Brief History of Semiconductors: the Foundry Transition

A modern fab can cost as much as $10B dollars. That’s billion with a B. Since it has a lifetime of perhaps 5 years, owning a fab costs around $50 per second and that’s before you buy any silicon or chemicals or design any chips. Obviously anyone owning a fab had better be planning on making and selling a lot of chips if they are going to make… Read More

A Brief History of FPGAs

From the transistor to the integrated circuit to the ASIC, next comes programmable logic devices on the road to the mainstream fabless semiconductor industry. PLDS started in the early 1970’s from the likes of Motorola, Texas Instruments, and IBM but it wasn’t until Xilinx brought us the field programmable gate array (FPGA)… Read More