Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Tag: vivado

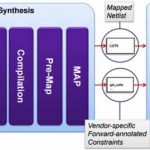

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

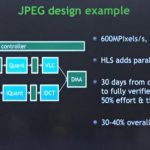

High Level Synthesis. Are We There Yet?

High level synthesis (HLS) seems to have been part of the backdrop of design automation for so long that it seems to be one of those things that nobody notices any more. But it has also crept up on people and gone from interesting technology to keep an eye on to getting genuine adoption. The first commercial product in the space was behavioral… Read More

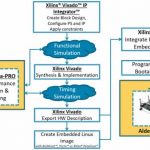

New Vivado release goes from Lab to UltraScale

Xilinx users will welcome the brand-new release of Vivado Design Suite 2015.1. For openers, device support for the latest FPGAs in the UltraScale family – XCVU440, XCVU190, and XCVU125 – has been added in the release, and early access code for the XCVU160 is available from a local Xilinx FAE. Installation has been streamlined, … Read More

Xilinx’s 16nm UltraScale+ FPGA is Revolutionary

Well a very belated Happy New Year dear reader. I must admit, it has been a very long winter and it has caused the Miller’s to rethink this vital question. “What in the world are we doing living in NY”. So we are moving, and hopefully this is my last ‘real’ winter as we headed down south. To perhaps alleviate some of the winter blues from … Read More

New Vivado Release. And a Competition!

It is not entirely clear what Xilinx is these days. Of course it is an FPGA company. If you hear the word FPGA then I bet Xilinx is the first thing you think of. But what Xilinx ships these days is a far cry from the type of device it created when it was starting, where FPGAs were largely used to vacuum up all the glue logic around the processors… Read More

Xilinx the EDA Company

Like you I cannot believe 2015 is upon us. 15 years ago I remember the Y2K panic. I remember watching the news and noticed the liberal media (they were liberal back then too) just waiting for the first fail somewhere. Ended up like Geraldo at the opening of Al Capone’s Vault. Remember that one? As I persist on with this word salad may I … Read More

Xilinx Boards Make a Great Christmas Gift!

Ok, first thing first, Happy Thanksgiving! For the Miller’s as I get older, it is new traditions as some old ones have passed on. Memories are great and new ones to make. So you know the great debate right?

These poor people working Thanksgiving to sell some tablet or smart phone to save a few bucks. Those that must work, my condolences… Read More

Xilinx Announces SDAccel, Accelerators for the Datacenter

Today Xilinx announced SDAccel, an initiative for the data-center. This is the second of a series of software defined development initiatives for various markets, the first being SDNet that is targeted at building networking applications. One challenge that a company like Xilinx faces is that as the scale of design move up to … Read More

Xilinx UltraFast Design Methodology Guide will save you time and money

Well today, i’m easing my way back in from vacation. Took a camper, 6 kids, 1 wife with bun in the oven and saw the great USA. 17 States, roughly 5500 miles. It was great fun and tiring at the same time. The Grand Canyon was a blessing but I really enjoyed the ‘The Four Corners‘ where UT, CO, NM, AZ all meet. I had each kid… Read More