When I first heard the term ‘bespoke silicon,’ I had to get my dictionary out. Well versed in the silicon domain, I did not know what bespoke meant. It turns out to be a rather old-fashioned term for tailor made and seems to be very much British English. The word dates from 1583 and is the past participle of bespeak, according… Read More

Tag: vhdl

Verific Sharpening the Saw

Verific is an unusual company. They are completely dominant in what they do – providing parsers for Verilog/SV, VHDL and UPF. Yet they have no ambition to expand beyond that goal. Instead, per Michiel Ligthart (President and COO), they continue to “sharpen the saw”. This is an expression I learned in sales training, habit #7 from… Read More

COO Interview: Michiel Ligthart of Verific

Today, Semiwiki profiles Verific Design Automation, perhaps the most popular company at DAC (when it’s an in-person event) because of its giveaway –– a 10”stuffed giraffe for anyone who walks up to its booth and listens to its story.

But, Verific is also a popular EDA company for more reasons than its tradeshow giveaway.… Read More

Why I made the world’s first on-demand formal verification course

Verification Challenge

As chip design complexity continues to grow astronomically with hardware accelerators running riot with the traditional hardware comprising CPUs, GPUs, networking and video and vision hardware, concurrency, control and coherency will dominate the landscape of verification complexity for safe … Read More

The Polyglot World of Hardware Design and Verification

It has become a cliché to start a blog post with a cliché, for example “Chip designs are forever getting larger and more complex” or “Verification now consumes 60% of a project’s resources.” Therefore, I’ll open this post with another cliché: “Designers need to know only one language, but verification engineers must know many.”… Read More

Mixed-Signal Debugging Gets a Boost

Having the right tool for the job at hand is always a joy, and when your IC project involves RTL code, gates, transistors and even parasitic interconnect, then you need some EDA tool help for debugging and finding out why your design behaves the way it is. An FAE named Sujit Roy did a conference call with me last week to show what StarVision… Read More

Webinar: Designing Complex SoCs and Dealing with Multiple File Formats

In SoC design it’s all about managing complexity through modeling, and the models that make up IC designs come in a wide range of file formats like:

- Transistor-level , SPICE

- Interconnect parasitics, SPEF

- Gate and RTL, Verilog, VHDL

Even with standard file formats, designers still have to traverse the hierarchy to find out… Read More

Foundational Excellence in a Laid-Back Style

I recently had a call with Rob Dekker, Founder and CTO of Verific. If you’re in EDA or semiconductor CAD, chances are high that you know who they are. They’re king of the hill in parser software for SystemVerilog and VHDL. When you hear a line like that, you assume a heavy dose of marketing spin, but here it really is fact. I don’t know of… Read More

Design Automation and the Engineering Workstation

This is the seventeenth in the series of “20 Questions with Wally Rhines”

Several common aspects have existed for what is now the modern Electronic Design Automation (EDA) industry. When I joined TI in 1972, the company was very proud of its design automation capability as a competitive differentiator. Much of the… Read More

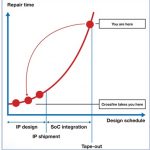

Crossfire Baseline Checks for Clean IP at TSMC OIP

IP must be properly qualified before attempting to use them in any IC design flow. One cannot wait to catch issues further down the chip design cycle. Waiting for issues to appear during design verification poses extremely high risks, including schedule slippage. For example, connection errors in transistor bulk terminals where… Read More