AMIQ EDA has caught my attention over the last few months. My first impression was that this was just another small IDE company trying to compete with established and bundled IDEs from the big 3, a seemingly insurmountable barrier. This view was challenged by an impressive list of testimonials, not just from the little guys but also… Read More

Tag: vhdl

A Picture is worth a 1,000 words

Semiconductor IP re-use is a huge part of the productivity gains in SoC designs, so instead of starting from a clean slate most chip engineers are re-using cells, blocks, modules and even sub-systems from previous designs in order to meet their schedule and stay competitive in the market place. But what happens when you intend to… Read More

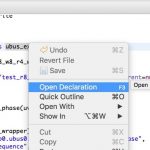

Getting More Productive Coding with SystemVerilog

HDL languages are a matter of engineering personal preference and often corporate policy dictates which language you should be using on your next SoC design. In the early days we used our favorite text-based editor like Vi or Emacs, my choice was Vi. The problem with these text-based editors of course is that they really don’t… Read More

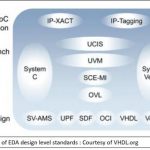

Why Open and Supported Interfaces Matter

Back in the early 1980’s during the nascent years of electronic design automation (EDA), I worked at Texas Instruments supporting what would become their merchant ASIC business. Back then, life was a bit different. The challenge we faced was to make our ASIC library available on as many EDA flows as we could to give as many users as… Read More

Improving on EMACS for VHDL Creation

OK – I admit I titled this piece as clickbait. There is a core of designers for whom belief in the supremacy of EMACS for RTL creation comes close to religion. Some will read only the title and jump immediately to penning searing comments questioning my intelligence, experience, parenthood and ability to tie my own shoes. Some, I hope,… Read More

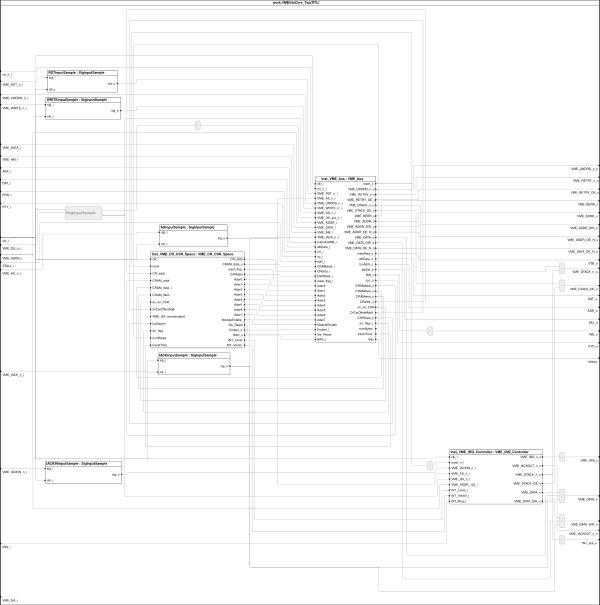

RTL Design Restructuring Explained

Modern SoC designs can use billions of transistors where transistors are grouped into gates, then gates grouped into cells, then cells grouped into blocks, blocks grouped into modules, and so on, creating a complex hierarchy. What a front-end designer conceives of logically for a hierarchy will differ from how an optimized physical… Read More

Pseudo random generator tutorial in VHDL (Part 3/3)

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

Pseudo random generator tutorial in VHDL (Part 2/3)

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

Pseudo random generator tutorial in VHDL (Part 1/3)

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

Dragging RTL Creation into the 21st Century

When I was at Atrenta, we always thought it would be great to do as-you-type RTL linting. It’s the natural use model for anyone used to writing text in virtually any modern application (especially on the Web, thanks to Google spell and grammar-checks). You may argue that you create your RTL in Vi or EMACS and you don’t need no stinking… Read More