With the increase in SoC designs’ sizes and complexities, the verification continuum has grown larger to an extent that the strategies for design convergence need to be applied from the very beginning of the design flow. Often designers are stuck with never ending iterations between RTL, gate and transistor levels at different… Read More

Tag: verification

Synopsys Software Integrity: Find All the Bugs

A couple of days ago Synopsys announced that they were acquiring Quotium’s product Seeker. This is an interactive application security testing (IAST) product. Synopsys are acquiring the product and the R&D team, not the whole of Quotium. The Seeker solution is a pioneering solution for IAST that helps businesses find high-risk… Read More

Experts Talk at Mentor Booth

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

SoC Debugging Just Got a Speed Boost

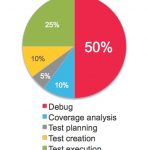

Sure, design engineers can get more attention than verification engineers, but the greater number of verification engineers on SoC projects means that the verification task is a bigger bottleneck in a schedule than pure design work. A recent survey conducted at Cadence shows how verification effort can be divided into several,… Read More

A Comprehensive Power Optimization Solution

In an electronic world driven by smaller devices packed with larger functions, power becomes a critical factor to manage. With power consumption leading to heat dissipation issues, reliability of the device can be affected, if not controlled or the device not cooled. Moreover, for mobile devices such as smartphones or tablets… Read More

Verification IP for PCIe and AXI4

Engineers love acronyms and my latest blog post has three acronyms in the title alone, so hopefully you are doing or considering SoC designs with the AMBA AXI4(Advanced eXtensible Interface 4) interface specification along with PCI Express (Peripheral Component Interconnect Express). One big motivation for using semiconductor… Read More

SystemC Co-Simulation of NoCs and IP Blocks

Verification in general suffers from a couple of fundamental problems. Availability of models and performance of different levels of representation.

The first problem, availability of models, is that you would like to start verification as soon as possible but all the representations are not ready early enough. Obviously … Read More

CDC Verification: A Must for IP and SoCs

In the modern SoC era, verification is no longer a post-design activity. The verification strategy must be planned much earlier in the design cycle; otherwise the verification closure can become a never ending problem. Moreover, verification which appears to be complete may actually be incomplete because of undetected issues… Read More

How many coats cover this SoC?

“Most interior paint covers with one coat.” Back when there was something called a newspaper, this was an actual blurb in the home improvement pages, section 3, part 8, page 5 of the Chicago Tribune on Sunday, August 13, 1961. Even then, marketers were catering to consumers looking to cut corners and save time, and one-coat coverage… Read More

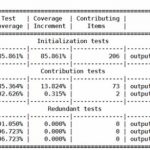

A Comprehensive Automated Assertion Based Verification

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More