You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

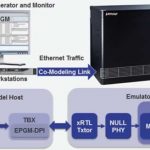

Verifying chip designs has always suffered from a two-pronged problem. The first problem is that actually building silicon is too expensive and too slow to use as a verification tool (when it happens, it is not a good thing and is called a “re-spin”). The second problem is that simulation is, and has always been, too slow.

When Xilinx… Read More

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

SmartDV started as a small setup in Bangalore in 2008 and by now is one of the most respectable VIP (Verification IP) companies in the world. Having a portfolio of 83 VIPs in its kitty and growing, it has a large customer base, including the top semiconductor companies around the world. The company has grown significantly and is raring… Read More

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

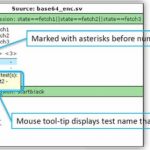

Continuous, incremental improvement based on customer feedback and insight from researchers is a pillar of the Aldec EDA strategy. Within the last two weeks, two of the Aldec product lines – Riviera-PRO, and ALINT-PRO-CDC – have seen new version releases. Here’s a quick look at some of the highlights of both.

Riviera-PRO 2015.06… Read More

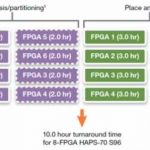

Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

The traditional system-on-chip (SoC) design process has fully qualified verification methods embodied in the form of process design kits (PDKs). Why is it that chip design companies and assembly houses have no IC/package co-design sign-off verification process?

Package die are often produced using multiple processes and… Read More

As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More

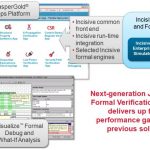

A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More