With the unprecedented increase in semiconductor design size and complexity design teams are required to accommodate multiple design constraints such as multiple power domains for low power design, multiple modes of operation, many clocks running, and third party IPs with different SDCs. As a result timing closure has become… Read More

Tag: verification

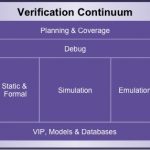

Synopsys Verification Continuum

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required… Read More

Transceiver Verification of a 20nm Altera FPGA Device

FPGA devices are a great way to drive silicon technology development because they contain both digital and analog IP, along with sophisticated IO cells. The highest performance IOs are transceivers, and Altera has recently designed the Arria 10 device family to include up to 96 transceivers, using a 20nm technology that can achieve… Read More

Automatic RTL Restructuring: A Need Rather Than Convenience

In the semiconductor design industry, most of the designs are created and optimized at the RTL level, mainly through home grown scripts or manual methods. As there can be several iterations in optimizing the hierarchy for physical implementation, it’s too late to do the hierarchical optimizations after reaching the floor plan… Read More

Another debug view in the UVM Toolbox

One of the biggest endearing qualities of a debug environment for any type of coding is availability of multiple ways to accomplish a task. Whether the preference is keyboard shortcuts, mouse left-click drill-down and right-click pull-down menus, source code view, hierarchical class view, or graphical relationship view, … Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

Then, Python walked in for verification

Go ahead – type “open source” into the SemiWiki search box. Lots of recent articles on the IoT, not so many on EDA tools. Change takes a while. It has only been about five years since the Big Three plus Aldec sat down at the same table to work on UVM. Since then, Aldec has also gotten behind OS-VVM, and is now linked to a relatively new open… Read More

Pizza con Questa

Last week I went to a lunch and learn at Mentor about their Questa formal product given by Kurt Takara. Like everyone else these days, Questa is packaged as a number of Apps for doing different tasks. Formal verification is different from other EDA tools in that different approaches can be used for different sub-tasks. There are three… Read More

Enterprise IP Management – A Whole New Gamut in Semiconductor Space

The world of IPs in the semiconductor landscape has completely changed the semiconductor design scenario, specifically the fabless design space. Today IPs are key components of any large semiconductor design, in the same way as auto ancillaries in auto design. It’s just the beginning, in the days to come we will see SoCs just as… Read More

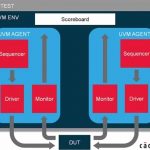

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More