To fans of Godel, Escher and Bach (the Eternal Golden Braid), there is an appealing self-referential elegance to the idea of verifying a network switch in a cloud-like resource somewhere on the corporate network. That elegance quickly evaporates however when you consider the practical realities of verifying such device in ICE… Read More

Tag: veloce

How Virtualization Makes Network Processor Verification Efficient

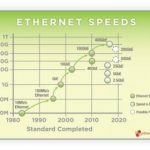

When Ethernet was introduced in 1983 it ran at 10Mbps and mostly relied on hubs and coaxial cable. Twelve years later a faster speed was introduced, running at 100Mbps. Since then we have seen an acceleration of new data rate introductions. According top the Ethernet Alliance, Ethernet could have 12 speeds before 2020, with 6 of … Read More

IoT chipsets and enterprise emulation tools

When most people talk about the IoT, it is usually all about wearables-this and low-power-that – because everyone is chasing the next huge consumer post-mobile device market. Mobile devices have provided the model. The smartphone is the on-ramp to the IoT for most consumers, with Bluetooth, Wi-Fi, and LTE, and maybe a dozen or … Read More

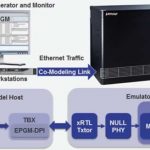

Testing Ethernet with virtual co-modeling

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

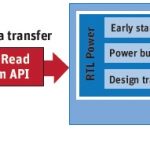

Power Analysis Needs Shift in Methodology

It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier … Read More

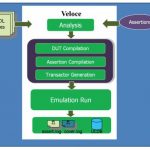

How PowerArtist Interfaces with Emulators

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

Getting the Best Dynamic Power Analysis Numbers

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

Virtual Emulation Extends Debugging Over Physical

Amid burgeoning complexity of SoC verification with ever increasing hardware, software and firmware content, verification engineers are hard pressed with learning multiple tools, technologies and methodologies and still completing SoC verification with full accuracy in time. The complexity, size and diversity of SoC … Read More

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More