Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

Tag: validation

Maybe not the world, but schedules got eaten

It has been almost five years since Marc Andreessen wrote the words, “Software is eating the world.” The premise of his essay in the Wall Street Journal in 2011 was pretty simple: the technology world has seen its intrinsic value shift from hardware to software. New all-software names have appeared on the list of high flying companies,… Read More

Should there be a 5-second IoT chip rule?

Kids have a tendency to put things in their mouths. Any parent can relate to the statement, “Put that down! You don’t know where it’s been!” After the first child, concern usually relaxes quite a bit. People joke about a 5-second rule on the premise if an object was just dropped on the floor, it may not be contaminated yet.… Read More

Secret Sauce of SmartDV and its CEO’s Vision

SmartDV started as a small setup in Bangalore in 2008 and by now is one of the most respectable VIP (Verification IP) companies in the world. Having a portfolio of 83 VIPs in its kitty and growing, it has a large customer base, including the top semiconductor companies around the world. The company has grown significantly and is raring… Read More

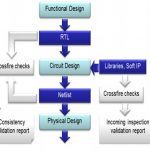

Semiconductor IP Validation Gets Faster

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort.… Read More

Semiconductor Strategy – From Productivity to Profitability

The semiconductor industry seems to be the most challenged in terms of cost of error; a delay of 3 months in product development cycle can reduce revenue by about 27% and that of 6 months can reduce it by almost half; competition is rife, pushing the products to next generation (with more functionality, low power, high performance,… Read More

12m FPGA prototyping sans partitioning

FPGA-based prototyping brings SoC designers the possibility of a high-fidelity model running at near real-world speeds – at least until the RTL design gets too big, when partitioning creeps into the process and starts affecting the hoped-for results.

The average ASIC or ASSP today is on the order of 8 to 10M gates, and that includes… Read More

Formally verifying protocols

I attended much of the Jasper users’ group a week ago. There were several interesting presentations that I can’t just blog about because companies are shy, and some that would only be of interest if you were a user of Jasper’s products on a daily basis.

But for me the most interesting presentations were several… Read More