In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

Tag: uvm

Then, Python walked in for verification

Go ahead – type “open source” into the SemiWiki search box. Lots of recent articles on the IoT, not so many on EDA tools. Change takes a while. It has only been about five years since the Big Three plus Aldec sat down at the same table to work on UVM. Since then, Aldec has also gotten behind OS-VVM, and is now linked to a relatively new open… Read More

Accelerating SoC Verification Through HLS

Once upon a time there was a struggle for verification completion of semiconductor designs at gate level. Today, beyond imagination, there is a struggle to verify a design with billions of gates at the RTL level which may never complete. The designs are large SoCs with complex architectures and several constraints of area, performance,… Read More

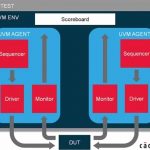

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More

Now even I can spot bad UVM

Most programmers can read a code snippet and spot errors, given enough hours in the day, sufficient caffeine, and the right lens prescription. As lines of code run rampant, with more unfamiliar third-party code in the mix, interprocedural and data flow issues become more important – and harder to spot.

Verification IP particularly… Read More

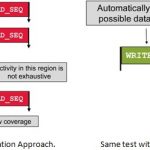

Effective Verification Coverage through UVM & MDV

In the current semiconductor design landscape, the design size and complexity of SoCs has grown to large extent with stable tools and technologies that can take care of integrating several IPs together. With that mammoth growth in designs, verification flows are evolving continuously to tackle the verification challenges … Read More

SoC Verification Closure Pushes New Paradigms

In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More

Cadence & ARM Optimize Complex SoC Performance

Now a day, a SoC can be highly complex, having 100s of IPs performing various functionalities along with multi-core CPUs on it. Managing power, performance and area of the overall semiconductor design in the SoC becomes an extremely challenging task. Even if the IPs and various design blocks are highly optimized within themselves,… Read More

Cadence Grows VIP Business – What’s New?

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

Constrain all you want, we’ll solve more

EDA tool development is always pushing the boundaries, driven in part by bigger, faster chips and more complex IP. For several years now, the trend has been developing tools that spot problems faster without waiting for the “big bang” synthesis result that takes hours and hours. Vendors, with help from customers, are tuning tools… Read More