I’m at the GSA Silicon Summit today, at the computer history museum. The first panel session this morning was about future process technology. It was moderated by Joe Sawicki of Mentor with a panel consisting of Rob Aitken from ARM, Paul Farrar of G450C, Peter Huang of TSMC, John Kibarian of PDF Solutions and someone from Applied… Read More

Tag: tsmc

What is Next for GLOBALFOUNDRIES?

In response to changing industry dynamics, AMD announced in October 2008 a new strategy to focus exclusively on the design phase of semiconductor product development. To achieve that strategy, AMD partnered with Advanced Technology Investment Company (ATIC) of Abu Dhabi to create a new joint venture company designed to become… Read More

FinFET Custom Design

At CDNLive, Bob Mullen of TSMC gave a presentation on their new custom FinFET flow, doing design, and verifying designs. At 16nm there are all sorts of relatively new verification problems such as layout dependent effects (LDE) and voltage dependent design rules. We had some of this at 20nm but like most things in semiconductor,… Read More

The Infamous Intel FPGA Slide!

As I have mentioned before, I’m part of the Coleman Research Group so you can rent me by the hour to better understand the semiconductor industry. Most of the conversations are by phone but sometimes I do travel to the East Coast, Taiwan, Hong Kong, and China for face-to-face meetings. Generally the calls are the result of an event … Read More

Getting an MPW Quote on My iPhone

As I blogged about recently, eSilicon have completely automated the quote process for their MPW shuttle service. You can use an online interface that runs in the browser but there is also an app that you can download from the App Store.

So I decided I had a few million dollars to burn and I’d get myself my very own TSMC 20nm parts.… Read More

Dr. Cliff Hou, TSMC VP of R&D, Keynote

This will be my 30[SUP]th[/SUP] Design Automation Conference. I know this because my first DAC was the same year I got married and forgetting how many years you have been married can cost you half your stuff. I have known Cliff Hou for half of that time and he has proven to be one of the most humble and honorable men I have worked with, definitely.… Read More

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More

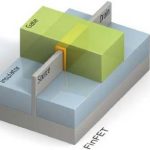

Designing an SoC with 16nm FinFET

IC designers contemplating the transition to 16nm FinFET technology for their next SoC need to be informed about design flow and IP changes, so TSMC teamed up with Cadence Design Systems today to present a webinar on that topic. I attended the webinar and will summarize my findings.

Shown below is a 3D layout concept of an ideal FinFET… Read More

The Great Wall of TSMC

TSMC doesn’t just sell wafers, it sells trust. It’s the Colgate Ring of Confidence for fabless customers. This focus on trust started at the very beginning when Morris Chang founded TSMC over 25 years ago, and still today trust remains an essential part of their business.

When TSMC started, the big thing it brought … Read More

Why Intel 14nm is NOT a Game Changer!

On one hand the Motley Fool is saying, “Intel 14nm could change the game” and on the other hand the Wall Street Cheat Sheet is saying, “Intel should shut down mobile”. SemiWiki says Intel missed mobile and should look to the future and focus on wearables and in this blog I will argue why.

Let’s look back to 2009 when Intel and TSMC signed… Read More