The fabless movement was instrumental in disaggregating the semiconductor industry. Vertical product development at the chip and system level has given way to a horizontal structure over the years. This organization of product development has been doing an admirable job of delivering extremely reliable products. However… Read More

Tag: tsmc

Standard Node Trend

I have previously published analysis’ converting leading edge logic processes to “standard nodes” and comparing standard nodes by company and time. Recently updated details on the 7nm process node have become available and in this article, I will revisit the standard node calculations and trends.… Read More

Designing at 7nm with ARM, MediaTek, Renesas, Cadence and TSMC

The bleeding edge of SoC design was on full display last month at DAC in Austin as I listened to a panel session where members talked about their specific experiences so far designing with the 7nm process node. Jim Hogan was the moderator and the panel quickly got into what their respective companies are doing with 7nm technology already.… Read More

Exclusive – GLOBALFOUNDRIES discloses 7nm process detail

In a SemiWiki EXCLUSIVE – GLOBALFOUNDRIES has now disclosed the key metrics for their 7nm process. As I previously discussed in my 14nm, 16nm, 10nm and 7nm – What we know now blog GLOBALFOUNDRIES licensed their 14nm process from Samsung and decided to skip 10nm because they thought it would be a short-lived node. At … Read More

TSMC Unveils More Details of Automotive Design Enablement Platform

At this year’s Design Automation Conference (DAC), TSMC unveiled more details about the design enablement platforms that were introduced at their 23[SUP]rd[/SUP] annual TSMC Technology Symposium earlier this year. I attended a presentation on TSMC’s Automotive Enablement Platform held at the Cadence Theater where TSMC’s… Read More

First Thoughts from #54DAC!

This was my 34[SUP]th[/SUP] DAC, yes 34. It is a shame blogging did not exist back then because I would have liked to have read thoughts from my eager young mind, or maybe not. The first thing that struck me this year is the great content. Before DAC I review the sessions I want to see and this year there were many more than I had time for. … Read More

TSMC @ #54DAC!

TSMC has been an ardent supporter of DAC for the last 18 years which has brought in the other foundries because, as the industry leader, wherever TSMC goes the other foundries naturally follow. The exception of course is Intel Custom Foundry because they march to the beat of a different drummer, if you know what I mean. The CoFluent… Read More

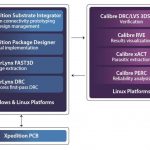

Tools for Advanced Packaging Design Follow Moore’s Law, Too!

There is an emerging set of advanced packaging technologies that enables unique product designs, with the capability to integrate multiple die, from potentially heterogeneous technologies. These “system-in-package” (SiP) offerings provide architects with the opportunity to optimize product performance, power, cost,… Read More

SEMICON Southeast Asia reflects strong equipment market

SEMICON Southeast Asia was held this week in Penang, Malaysia. Over 6500 people attended the conference to learn about the latest trends and equipment in semiconductor manufacturing.

Dr. Dan Tracy, Senior Director Industry Research and Statistics at SEMI, presented an optimistic outlook for the semiconductor equipment market… Read More

Live from the TSMC Earnings Call!

Last week I was invited to attend the TSMC earnings call at the Shangri-la Hotel in Taipei which was QUITE the experience. I generally listen in on the calls and/or read the transcripts but this was the first one I attended live. I didn’t really know what to expect but I certainly did NOT expect something out of Hollywood. Seriously,… Read More