Unique device identities are at the core of all computer security systems. Just as important is that each unique identity cannot be copied, because once copied they can be used illegitimately. Unique device IDs are used to ensure that communications are directed to the correct device. And they also provide the ability to encrypt… Read More

Tag: sram

Adapting an embedded FPGA for Aerospace Applications

The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment,… Read More

Arm TechCon Preview with the Foundries!

This week Dr. Eric Esteve, Dr. Bernard Murphy, and I will be blogging live from Arm TechCon. It really looks like it will be a great conference so you should see some interesting blogs in the coming days. One of the topics I am interested in this year is foundation IP and I will tell you why.

During the fabless transformation of the semiconductor… Read More

Embedded FPGA Blocks as Functional Accelerators (AMBA Architecture, with FREE Verilog Examples!)

A key application for embedded FPGA (eFPGA) technology is to provide functionality for specific algorithms — as the throughput of this implementation exceeds the equivalent code executing on a processor core, these SoC blocks are often referred to as accelerators. The programmability of eFPGA technology offers additional… Read More

Noise, The Need for Speed, and Machine Learning

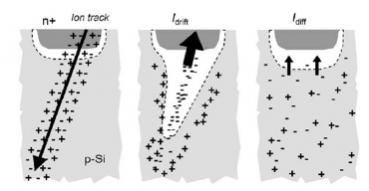

Technology trends make the concerns with electronic noise a primary constraint that impacts many mainstream products, driving the need for “Design-for-Noise” practices. That is, scaling, and the associated reduction in the device operating voltage and current, in effect magnifies the relative importance of non-scalable… Read More

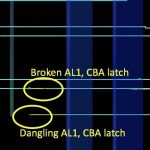

Calibre Can Calculate Chip Yields Correlated to Compromised SRAM Cells

It seems like I have written a lot about SRAM lately. Let’s face it SRAM is important – it often represents large percentages of the area on SOC’s. As such, SRAM yield plays a major role in determining overall chip yields. SRAM is vulnerable to defect related failures, which unlike variation effects are not Gaussian in nature. Fabrication… Read More

SRAM Optimization Saves Power on SOC’s and in Systems

Mobile device designers face the dilemma of reducing power and at the same time maintaining or increasing performance. Consumers will not tolerate increased battery life at the expense of performance. If it were otherwise, designers could simply dial back clock rates. Without this simple cure, the best way to reduce power for… Read More

TSMC Design Platforms Driving Next-Gen Applications

Coming up is the 23rd annual TSMC Technology Symposium where you can get first-hand updates on advanced and specialty technologies, advanced backend capabilities, future development plans, and network with hundreds of TSMC’s customers and partners. This year the Silicon Valley event kicks off at the Santa Clara Convention… Read More

CEO Interview: Geoff Tate of Flex Logix

This is the second in series of interviews we will do with executives inside the fabless semiconductor ecosystem. Geoff Tate was the founding CEO of Rambus and is now CEO and co-founder of Flex Logix (embedded FPGA). This one should be of great interest due to the recent $16.7B acquisition of Altera by Intel. We all now know the importance… Read More

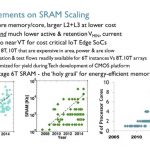

Statistical Simulation Provides Insight into 6T SRAM Optimization

ARM’s Azeez Bhavnagarwala recently gave a talk hosted by Solido on the benefits of variation aware design in optimizing 6T bit cells. Azeez sees higher clock rates, increasing usage of SRAM per processor and the escalating number of processors, shown in the diagram below, as trends that push designers toward 6T. Six Transistor… Read More