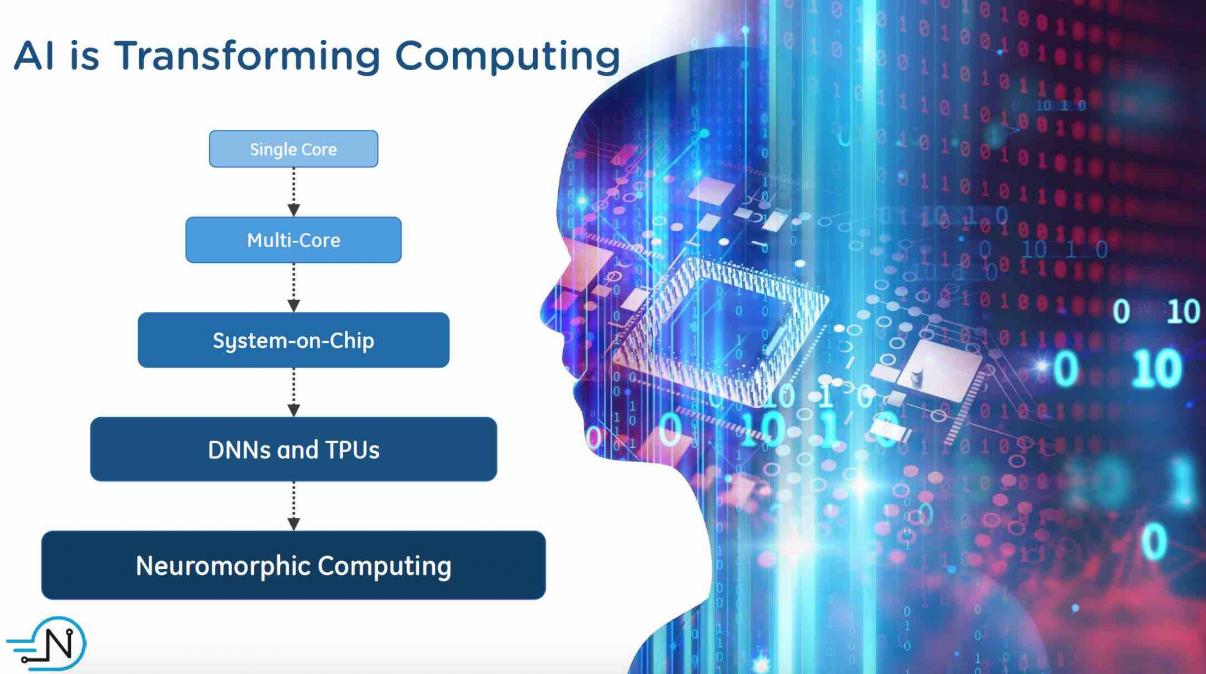

Artificial Intelligence based systems are driving a metamorphosis in computing, and consequently precipitating a large shift in SOC design. AI training is often done in the cloud and has requirements for handling huge amounts of data with forward and backward data connections. Inference usually occurs at the edge and must be… Read More

Tag: soc

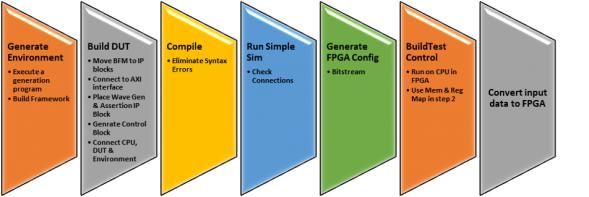

The 4th Way Beyond Simulation, FPGA Synthesis, and Emulation

As verification continues to be a key ingredient in successful design implementation, new approaches have been tried to balance cost, time to results and comprehensive analysis in designs that require large patterns in some application like Image Processing. Simulation environments are well proven, and designers tend to … Read More

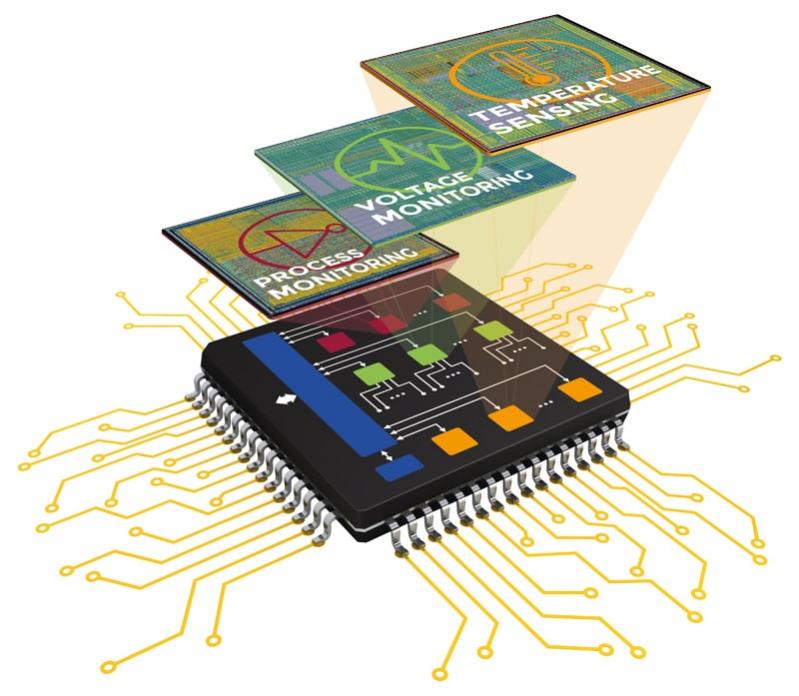

Webinar Alert – Embedded Monitoring of Process and Voltage in SoCs

In the old days to learn about new semiconductor IP you would have to schedule a sales call, listen to the pitch, then decide if the IP was promising or not. Today we have webinars which offer a lot less drama than a sales call, plus you get to ask your questions by typing away at the comfort of your desk, hopefully wearing headphones as … Read More

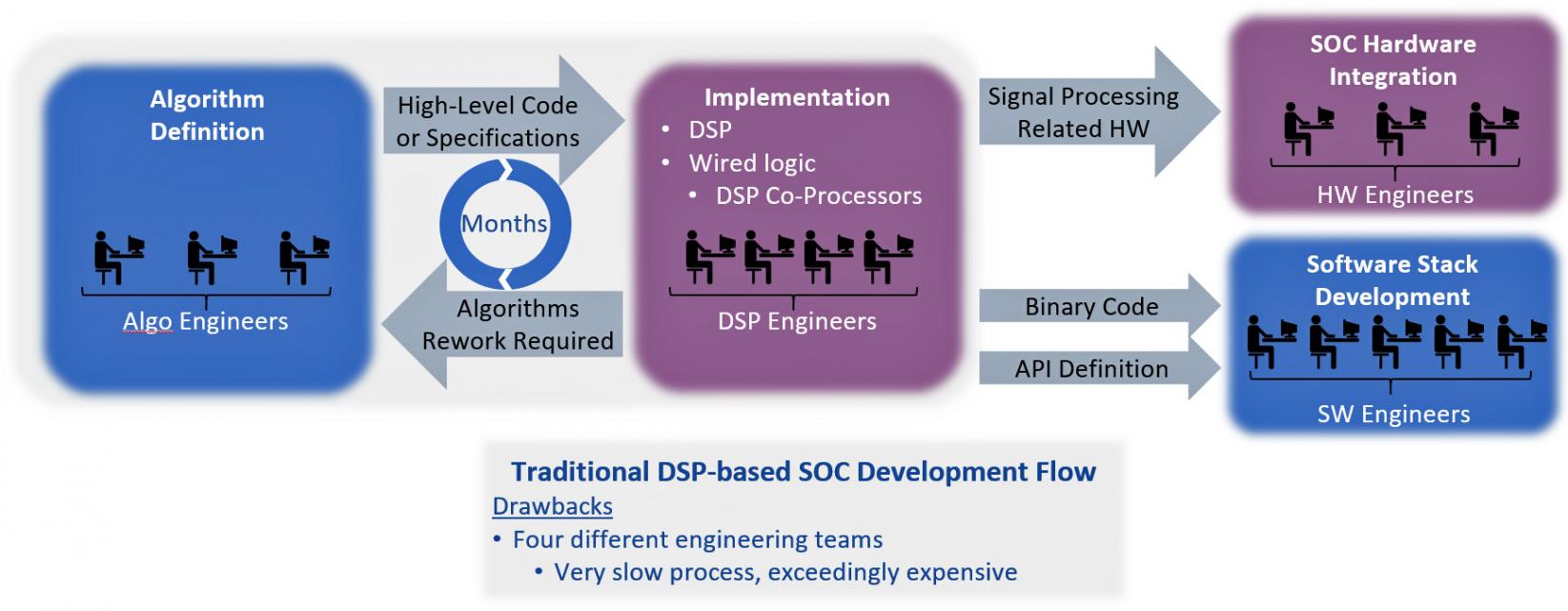

DSP SoC a la Française

I enjoyed reading Eric Esteve’s article “ French Tech at CES, 2nd country after USA with 274 Start-Up at Eureka Park!” It brought back happy memories of my time at EVE until Synopsys purchased it in 2012.Here is another intriguing story by a French startup named VSORA and founded by Khaled Maalej with a team of scientists and engineers.… Read More

IoT Designs Beginning to Shift to 7nm: Promises Upside for Cadence Physically-Aware Design Flow

Until recently, ICs at bleeding edge nodes like 7nm technology from foundries like TSMC were mostly targeted for high-performance-computing (HPC) and mobile applications or possibly high radix switches that needed the increased performance of advanced nodes. The momentum of Moore’s law and Moore-than-Moore saw foundries… Read More

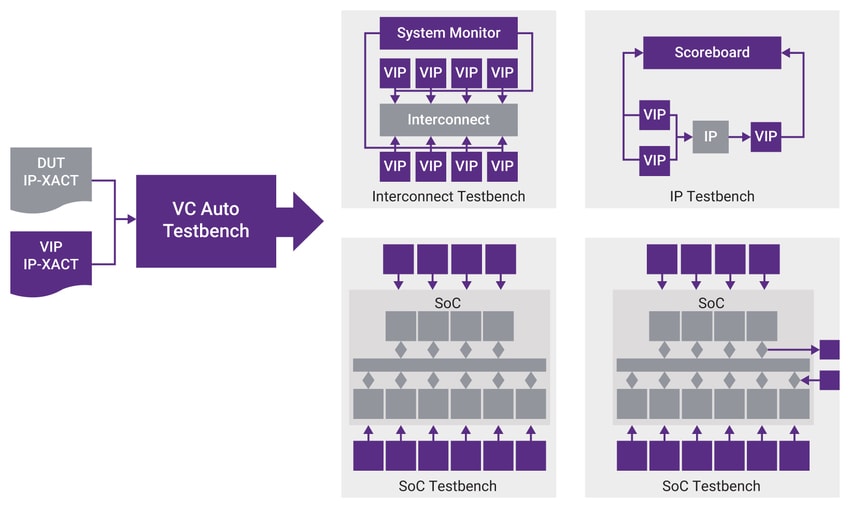

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

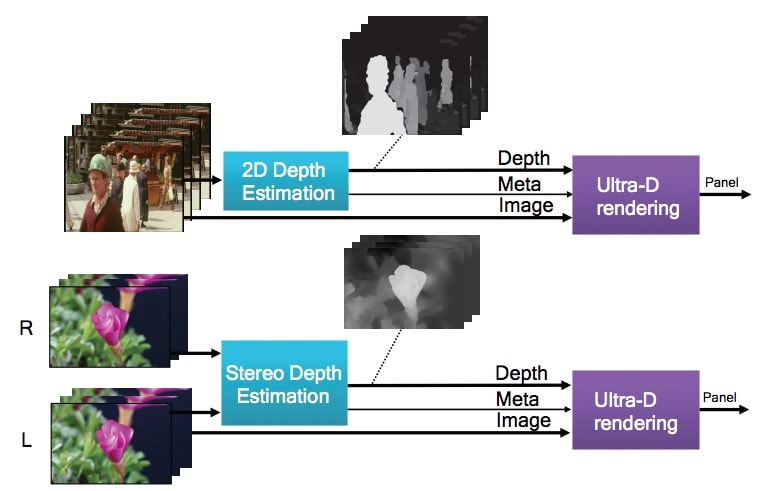

Designing an SoC for 3D TV Without using the Funny Glasses

In the blur of activities at DAC last year I visited the Mentor booth a few times and had just a few minutes to glance at a 3D TV display that didn’t require me to wear any funny glasses, kind of novel I thought at the time because I’ve read that the market of 3D TV sets is being hampered by requiring viewers to wear glasses. The… Read More

Scoreboard and Issues Management Tools for PCB Projects

The complexity of an SoC design necessitates that the project managers have accurate visibility into the overall design status, spanning the entire range of tasks – from functional simulation error triage, to physical layout verification errors, to electrical analysis results. Flow scripts used by SoC teams parse the log file… Read More

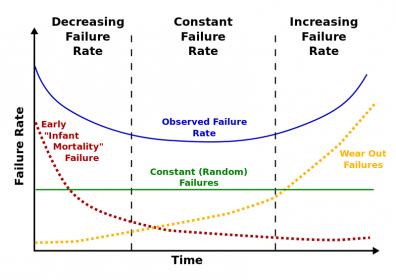

Neural Networks Leverage New Technology and Mimic Ancient Biological Systems

Neural networks make it possible to use machine learning for a wide variety of tasks, removing the need to write new code for each new task. Neural networks allow computers to use experiential learning instead of explicit programming to make decisions. The basic concepts related to neural networks were first proposed in the 1940’s,… Read More

TechCon: See ANSYS and TSMC co-present

ANSYS and TSMC will be co-presenting at ARM TechCon on Multiphysics Reliability Signoff for Next Generation Automotive Electronics Systems. The event is on Thursday October 26th, 10:30am-11:20am in Grand Ballroom B.

You can get a free Expo pass which will give you access to this event HERE and see the session page for the event … Read More