Timing exceptions are ways of guiding design tools, primarily synthesis and static timing analysis (STA), but these days also place & route and perhaps other tools. Most paths in a design go from one register to the next register. Both registers are on the same clock, and the design needs to ensure that the signal can make it from… Read More

Tag: soc

Xilinx picks another winner…

Just as important as block RAMs, IO and DSP48’s is what interconnect or fabric is going to be used when considering SoC FPGA designs. I think Xilinx has found the winning combination. What is paramount to the new SoC FPGA methodologies is not only the challenge of moving huge amounts of data around; we are now to consider data… Read More

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

From Layout Sign-off to RTL Sign-off

This week, I had a nice opportunity meeting Charu Puri, Corporate Marketing and Sushil Gupta, V.P. & Managing Director at Atrenta, Noida. Well, I know Sushil since 1990s; in fact, he was my manager at one point of time during my job earlier than Cadence. He leads this large R&D development centre, consisting about 200 people… Read More

The FPGA Blob is Coming…

I never understood when I was a kid how ‘the Blob’ could actually catch someone but it sure did. It caught the unsuspecting, the off guard. I mean you’d have time for a soda and shower if you saw it on your road. And no, your manager is not the Blob; don’t think like that, it’s always his boss. The blob comes to consume the worker who was unaware… Read More

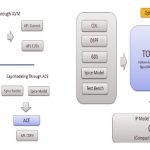

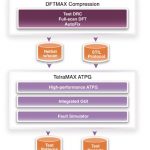

Minimize the Cost of Testing ARM® Processor-based Designs and Other Multicore SoCs

On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single… Read More

SoC Constraints, Design & Verification at DAC

I hadn’t followed EDA start-up company Ausdiamuch before, so at DAC I met with Sam Appleton, CEO to find out what they are all about.

Sanjay Lall, Sam Appleton – Ausdia

… Read More

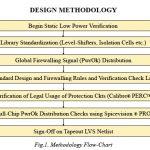

Static Low-Power Verification in Mixed-Signal SoC Designs

IC designer Shubhyant Chaturvediof AMD used EDA tools from Mentor Graphicsand Concept Engineeringto perform static, low-power verification of a mixed-signal SoC design with a combined CPU and GPU. Shubhyant presented a poster session at DAC two weeks ago in Austin, and I wanted to share it with my readers here at SemiWiki.… Read More

Deploying 14nm FinFETs in your Next Mobile SoC

At DAC in Austin a design company, foundry and EDA vendor teamed up to present their experiences with 14nm FinFETs during a breakfast on Tuesday.

Panelists included:

- Ed Sperling, Semi Mfg and Design

- Anil Jain, Cavium

- Subramani Kengeri, GLOBALFOUNDRIES

- Kelvin Low, GLOBALFOUNDRIES

- Raymond Leung, Synopsys

- Bari Biswas, Synopsys

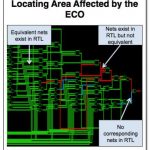

Formality Ultra, Streamline Your ECOs

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More