The semiconductor industry seems to be the most challenged in terms of cost of error; a delay of 3 months in product development cycle can reduce revenue by about 27% and that of 6 months can reduce it by almost half; competition is rife, pushing the products to next generation (with more functionality, low power, high performance,… Read More

Tag: soc

How to meet 3Ps in 3D-ICs with sub-20nm Dies?

It feels to be at the top of semiconductor technology by having dies with high density of semiconductor design at sub-20nm technology node stacked together into a 3D-IC to form a complete SoC which can accommodate billions of gates. However there are multiple factors to be looked at in order to make that successful amid often conflicting… Read More

Mixed-Signal SoC Debugging & IP Integration Made Easy

A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

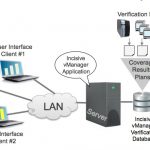

SoC Functional Verification Planning and Management Goes Big

Big SoC designs typically break existing EDA tools and old methodologies, which then give rise to new EDA tools and methodologies out of necessity. Such is the case with the daunting task of verification planning and management where terabytes of data have simply swamped older EDA tools, making them unpleasant and ineffective… Read More

Xilinx: Delivering a Generation Ahead

Last week was Xilinx’s investor day. Xilinx believe they are now a process generation ahead. They did over $100M in 28nm designs in FY2013 (Xilinx FY ended March 2013) and did over over $100M in Q4 2013 calendar year alone (and this is almost all true production volume, with only about 5% prototypes) with a plan greater than … Read More

Carbon Design Systems – Secret of Success

Last week, after learning from the press releaseof Carbonabout its rocking sustained growth with record-breaking revenue and a thumping 46% increase in bookings, I was interested to know some more details about what drives Carbon to such an amazing performance in an EDA market that is generally prone to growth of a few percentage… Read More

Power Control Moving into Hardware

Sonics have been building networks-on-chips (NoCs) for a long time and have amassed a rich patent portfolio. So being granted a new one isn’t usually deemed press-release-worthy. However, their latest patent on power management is pretty significant. It is patent 8,601,288 titled “Intelligent Power Controller”.

Historically… Read More

Happy Birthday Xilinx

I have never done this before, wished a company happy birthday. So here goes, Happy Birthday Xilinx! How does it feel to be 30? Looking good eh? Signing up for AARP? My family and I just sang and had cake and ice cream. They did look at me like I was nuts when I set a place at the table for a Xilinx FPGA. In all seriousness, over the years Xilinx… Read More

Will Google Design Server SoCs?

Google is search, of course, but it is also OS (Android), systems (Glass) and increasingly, maybe, hardware. Rumors are swirling that through careful acquisitions and focused internal development, Google is set to make its own server SoCs.

Google’s Larry Page has stated that they are in the hardware business. They’ve been making… Read More

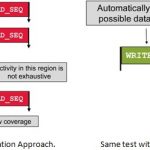

SoC Verification Closure Pushes New Paradigms

In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More