When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

Tag: soc

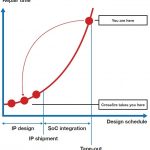

Foolproof Your IP before it Stumbles in Higher-up Design

SoC designs are increasingly becoming assemblies of a large number of IP blocks. A well integrated assembly can lead to a successful PPA (Power, Performance and Area) optimized design. However, it is equally important that each IP block is optimized, robust, and integrable in the design. The complexity of an IP and its integration… Read More

A Key Aspect Missing for IoT to become NBT

The IoT (Internet of Things) is not one product, technology, segment, or market. It’s a combination of many things, many markets, and many technologies. However, it’s one thing that needs to connect everything together; edge device to gateway to cloud. That brings the complexity, how’s that possible amid large heaps of heterogeneous… Read More

Build Low Power IoT Design with Foundation IP at 40nm

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

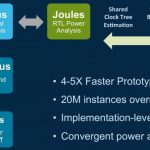

Power Analysis Needs Shift in Methodology

It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier … Read More

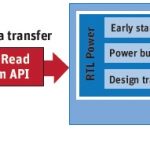

How PowerArtist Interfaces with Emulators

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

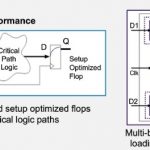

Leveraging Power Reduction Techniques for MCU Based SoCs

Dolphin Integration launched a new 32-bit microcontroller, RISC-351 Zephyr, targeting low-power SoCs for IoT-like competitive markets taking into consideration three angles for optimization of power consumption: architectural, memory and software.

Architecture Angle

As a reminder, 8-bit versus 16-bit versus 32-bit… Read More

How Emulation Enables Complex Power Intent Modeling

As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More

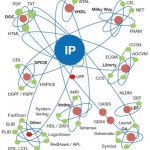

An Universe of Formats for IP Validation

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

New Tool Suite to Accelerate SoC Integration

Today, an SoC is seen in the context of an optimized assembly of IPs; it’s no more a single monolithic chip design. It’s very common to see an ARM processor IP along with an interconnect IP, a memory IP, and couple of buses and interfaces IP in an SoC. Although the SoC seems to be an integrated collection of IPs, it can be very complex and… Read More