You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

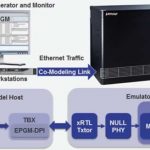

When it comes to predicting SoC performance in the early stages of development, most designers rely on simulation. For network-on-chip (NoC) design, two important factors suggest that simulation by itself may no longer be sufficient in delivering an optimized design.

The first factor is use cases. I think I’ve told the story … Read More

It has been four years since the announcement of the ARMv8 instruction set, three years since the launch of the ARM Cortex-A57 and Cortex-A53 cores, and two years since the Apple A7 with its “Cyclone” core blew away any misunderstanding of 64-bit as being just for servers.

There is, however, still this idea that 64-bit is only for … Read More

A mobile GPU is an expensive piece of SoC real estate in terms of footprint and power consumption, but critical to meeting user experience demands. GPU IP tuned for OpenGL ES is now a staple in high performance mobile devices, rendering polygons with shading and texture compression at impressive speeds.

Creative minds in the desktop… Read More

Most of the discussion around Xilinx UltraScale parts in FPGA-based prototyping modules has been on capacity, and that is certainly a key part of the story. Another use case is developing, one that may be even more important than simply packing a bigger design into a single part without partitioning. The real win with this technology… Read More

Most of us understand the basic concept of a virtual channel: mapping multiple channels of traffic, possibly of mixed priority, to a single physical link. Where priority varies, quality of service (QoS) settings can help ensure higher priority traffic flows unimpeded. SoC designers can capture the benefits of virtual channels… Read More

In the late 1990s and early 2000s, during the adolescent days of the system-on-chip (SoC) design movement, there was a lot talk about IP and design reuse, but it was seldom put into practice. A decade later, SoC turned into a juggernaut with a tripartite alliance of chipmakers, IP suppliers and semiconductor manufacturing fabs.… Read More

We’re putting the finishing touches on Chapter 9 of our upcoming book on ARM processors in mobile, this chapter looking at the evolution of Qualcomm. One of the things that made Qualcomm go was their innovative use of digital simulation. First, simulation proved out the Viterbi decoder (which Viterbi wasn’t convinced had a lot … Read More

If I grab 10 technologists and ask what are the most important issues surrounding the Internet of Things today, one of the popular answers will be “security.” If I then ask them what IoT security means, I probably get 10 different answers. Encryption. Transport protocols. Authentication. Keying. Firewalls. Secure boot. Over-the-air… Read More

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

SoC designers working on chips for the IoT and wearables now have access to cutting-edge certified Bluetooth Smart technology from CEVA. At Bluetooth ASIA in Shanghai, CEVA announced the RivieraWaves Bluetooth Smart 4.2 IP Platform has achieved full certification by the Bluetooth SIG to the Bluetooth 4.2 specification using… Read More