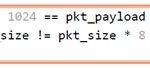

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

Tag: simulation

HW Emulator Apps Open Doors to Entirely New Uses

When the topic of hardware emulation comes up, thoughts of big iron customarily come to mind. However, hardware emulation has evolved significantly and now there are other important traits that distinguish the offerings in this area. For a very long period of time emulators provided primarily a method to accelerate gate level… Read More

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

Finding under- and over-designed NoC links

When it comes to predicting SoC performance in the early stages of development, most designers rely on simulation. For network-on-chip (NoC) design, two important factors suggest that simulation by itself may no longer be sufficient in delivering an optimized design.

The first factor is use cases. I think I’ve told the story … Read More

A moment of IoT silence before we disrupt

As I sat down in the SEMI Arizona Chapter breakfast meeting a few weeks ago, a moment of semiconductor history flew right before my eyes before the IoT sessions started.

We were seated in the cafeteria of Freescale Building 94 on Elliot Road in Tempe, a place I’d been many times before, except this time may have been the last. NXP is consolidating… Read More

Nine Cost Considerations to Keep IP Relevant –Part2

In the first part of this article I wrote about four types of costs which must be considered when an IP goes through design differentiation, customization, characterization, and selection and evaluation for acquisition. In this part of the article, I will discuss about the other five types of costs which must be considered to enhance… Read More

All Models Are Wrong, Some Are Useful

“All models are wrong, some are useful.” This remark is attributed to the statistician George Box who used it as the section heading in a paper published in 1976.

Just for fun I looked up a few semiconductor statistics from 1976. Total capital spending was $238M in Japan and $306M in US and…that’s it, there was nobody else back then … Read More

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

Secret Sauce of SmartDV and its CEO’s Vision

SmartDV started as a small setup in Bangalore in 2008 and by now is one of the most respectable VIP (Verification IP) companies in the world. Having a portfolio of 83 VIPs in its kitty and growing, it has a large customer base, including the top semiconductor companies around the world. The company has grown significantly and is raring… Read More

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More