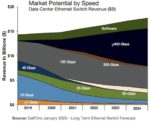

Ethernet speed evolution has kept a nice pace over the years even without any competing communications standard. And there are no signs of that slowing down, thanks to innovative companies deploying creative design techniques to keep delivering high-performance SerDes IP solutions. SerDes plays an integral role in implementing… Read More

Tag: serdes

How PCI Express 6.0 Can Enhance Bandwidth-Hungry High-Performance Computing SoCs

What do genome sequencing, engineering modeling and simulation, and big data analytics have in common? They’re all bandwidth-hungry applications with complex data workloads. High-performance computing (HPC) systems deliver the parallel processing capabilities to generate detailed and valuable insights from these applications.

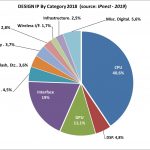

How SerDes Became Key IP for Semiconductor Systems

We have seen that the interface IP category is seeing incredibly high growth rate over the last two decades and we expect this category to generate an ongoing high source of IP revenues for at least another decade. But if we dig into the various successful protocols like PCI Express, Ethernet or USB, we can detect a common function … Read More

Alphawave IP is Enabling 224Gbps Serial Links with DSP

Alphawave IP is a new member of the SemiWiki community. You can learn about the company and their CEO, Tony Pialis in this interview by Dan Nenni. Design & Reuse did a virtual IP-SOC Conference recently and Tony presented. The D&R event had a very strong lineup of presenters. They supplemented the prepared video presentations… Read More

CEO Interview: Tony Pialis of Alphawave IP

Tony Pialis is a visionary entrepreneur focused on developing

technologies for next generation connectivity. In the last twenty 20 years, he has co-founded three semiconductor IP companies, all exclusively targeting connectivity IP. Tony is currently the CEO of Alphawave IP Inc, a leader in delivering multi-standard wireline… Read More

High Speed SerDes Design and Simulation Webinar Replay from Mentor

Over the years SerDes (serializer/deserializer) based connections have proliferated into just about every connection within and among computing systems. Years ago, parallel interfaces were the most common method of moving data, but issues of signal integrity, synchronization and power simply became too much for the required… Read More

Signal Channel Design and Simulation for Silicon Interposer Packaging on High-Speed SerDes

This year is the 25th anniversary for DesignCon. The show has changed a lot over the years. Today, it’s a vibrant showcase of all aspects of advanced product design – from ICs to boards to systems. The show floor reflects the diverse ecosystem. If you missed it this year, definitely plan to go next year.

The DesignCon technical program… Read More

#56thDAC SerDes, Analog and RISC-V sessions

The good news is that the next five DAC events will take place in Moscone Center in San Francisco! If going to Las Vegas from the Bay area is an easy trip, coming from Europe to Las Vegas makes it a 24+hours journey… One obvious consequence was the poor attendance to the exhibition floor. But let’s be positive and notice that the number… Read More

Monday DAC IP Session “PAM 4 Enable 112G SerDes”

This session will open the DAC IP Track at 10:30 on Monday “How PAM4 and DSP Enable 112G SerDes Design” in Room N264. I am very proud to chair this invited paper session, as it addresses one of the key pieces of design, enabling to exchange data flow at the highest possible data rate. It can be between two chips on the same board, we talk … Read More

eSilicon Bucking the Trend at OFC with 7nm SerDes

A recent press release from eSilicon caught my eye. The company has been touting their 7nm SerDes quite a bit lately – reach, power, flexibility, things like that. While those capabilities are important, any high-performance chip needs to work in the context of the system, which usually contains technology from multiple sources.… Read More