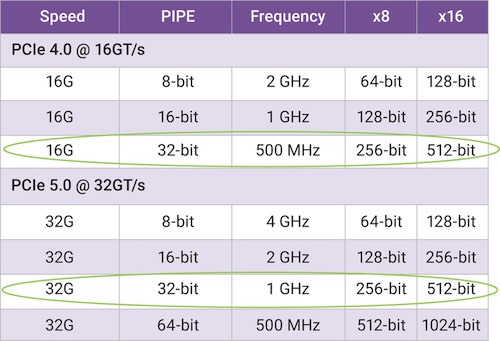

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

Tag: serdes

eSilicon Expands Expertise in 7nm

At SemiWiki we usually don’t write about the press releases we are sent. However, a recent press release by eSilicon caught my eye and prompted me to call Mike Gianfagna, eSilicon Vice President of Marketing. The press release is not just about one thing, rather it focuses on a number of interesting things that together show their… Read More

56G and 112G SerDes Where the rubber meets the road

No matter how high the processing capability of a chip, its overall performance is limited by IO speed. This is very similar to a car with low performance tires, a powerful engine will not be able to transfer its energy to the ground effectively. There is quite literally a race going on between core processing and IO speeds for transferring… Read More

RISC-V End to End Solutions for HPC and Networking

Semiconductor IP is one of the more exciting and most viewed topics we cover on SemiWiki, it has been that way since we began in 2011 and that trend will continue indefinitely, my opinion.

Semiconductor IP: Total Blogs: 640: Total Views: 3253751: Average: 5084

Based on the design starts we track, Cloud Computing is a leading semiconductor… Read More

Playing the Long Game with 56G SerDes

IP has always been a hot topic on SemiWiki with quite a bit of our readers doing the “make versus buy” analysis. SerDes is one of the more difficult “makes” so it is mostly a “buy” analysis made by networking class ASIC architects and a handful of other applications that demand high performance and throughput. Based on the recent traffic… Read More

Custom SoC Platform Solutions for AI Applications at the TSMC OIP

The TSMC OIP event is next week and again it is packed with a wide range of technical presentations from TSMC, top semiconductor, EDA, and IP companies, plus long time TSMC partner and ASIC provider Open-Silicon, a SiFive Company. You can see the full agenda HERE.

AI is revolutionizing and transforming virtually every industry… Read More

eSilicon and SiFive partner for Next-Generation SerDes IP

While writing “Mobile Unleashed: The Origin and Evolution of ARM Processors In Our Devices” it was very clear to me that ARM was an IP phenomenon that I did not believe would ever be repeated. Clearly I was wrong as we now have RISC-V with an incredible adoption rate, a full fledged ecosystem, and top tier implementers… Read More

Deep learning fueling the AI revolution with Interlaken IP Subsystem

AI is revolutionizing and transforming virtually every industry in the digital world. Advances in computing power and deep learning have enabled AI to reach a tipping point toward major disruption and rapid advancement. However, these applications require much higher performance and bandwidth requiring new kinds of IP and… Read More

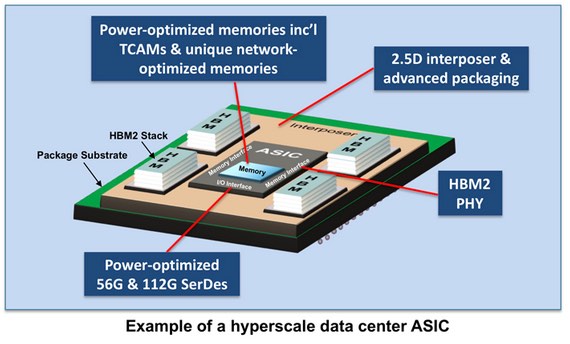

7nm Networking Platform Delivers Data Center ASICs

We all know IP is critical for advanced ASIC design. Well-designed and carefully tested IP blocks and subsystems are the lifeblood of any advanced chip project. Those IP suppliers who can measure up to the need, especially at advanced process nodes, will do well, absolutely.

It is interesting to note that eSilicon now has a very … Read More

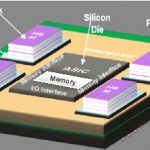

What does a Deep Learning Chip Look Like

There’s been a lot of discussion of late about deep learning technology and its impact on many markets and products. A lot of the technology under discussion is basically hardware implementations of neural networks, a concept that’s been around for a while.

What’s new is the compute power that advanced semiconductor technology… Read More