You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

TSMC’s technnology symposium seems to be the new time to make product announcements, with ARM and Atrenta yesterday and Springsoft today.

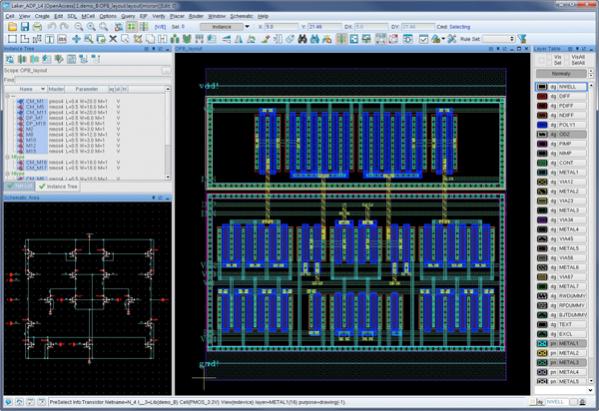

There is a new incarnation of Springsoft’s Laker layout family, Laker[SUP]3[/SUP] (pronounced three, not cubed). The original version ran on its own proprietary database.… Read More

My first IC design in 1978 was a 16Kb DRAM chip at Intel and our researchers discovered the strange failure of Soft Errors caused by Alpha particles in the packaging and neutron particles which are more prominent at higher altitudes like in Denver, Colorado. Before today if you wanted to know the Soft Error Rate (SER) you had to fabricate… Read More

Kurt Shuler from Arteris has written a short but useful blog about the various high speed interface protocols currently used in the wireless handset (and smartphone) IP ecosystem. Arteris is well known for their flagship product, the Network-on-Chip (NoC), and the Mobile Application Processor market segment represent the … Read More

Cloud computing is the talk of the tech world nowadays. I even hear commentaries about how entrepreneurs are turned down by venture capitalists for not including a cloud component into their business plan no matter what the core business may be. The commentary goes “It’s cloudy without any clouds.” Add some clouds to your strategy… Read More

Wally Rhines’ keynote at U2U, the Mentor users’ group meeting, was about Mentor’s strategy of focusing on what other people don’t do. This is partially a defensive approach, since Mentor has never had the financial firepower to have the luxury of focusing all their development on sustaining their products and then make … Read More

Oasys announced that it closed its series B funding round with investments from Intel Capital and Xilinx. The fact that any EDA company has closed a funding round is newsworthy these days; companies running out of cash and closing the doors seems to be a more common story.

Oasys has been relatively quiet, which some people have taken… Read More

EDPS: SoC FPGAsby Paul McLellan on 04-09-2012 at 4:00 amCategories: Events, FPGA

Mike Hutton of Altera spends most of his time thinking about a couple of process generations out. So a lot of what he worries about is not so much the fine-grained architecture of what they put on silicon, but rather how the user is going to get their system implemented. 2014 is predicted to be the year in which over half of all FPGAs will… Read More

Analyzing the operation of a modern SoC, especially analyzing its power distribution network (PDN) is getting more and more complex. Today’s SoCs no longer operate on a continuous basis, instead functional blocks on the IC are only powered up to execute the operation that is required and then they go into a standby mode, … Read More

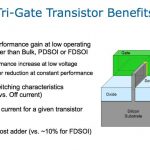

It was an honor to see DR. Chenming Huspeak and to learn more about FinFets, a technology he has championed since 1999. Chenming is considered an expert on the subject and is currently a TSMC Distinguished Professor of Microelectronics at University of California, Berkeley. Prior to that he was the Chief Technology Officer of TSMC.… Read More

Conquering the Big Data Challengesby Beth Martin on 04-02-2012 at 4:38 pmCategories: EDA, Siemens EDA

Extrapolating the trends from last 20 years to the next ten suggests that we will be implementing a trillion transistors or more by 2020. At 20nm, with the chip sizes touching billions of transistors, the age old problem of how to implement a design in the most efficient manner remains unanswered. … Read More