You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The Silicon Valley CDNLive, the Cadence user conference, will be on March 12-13th 2013 in Santa Clara. But the heart of CDNLive are customer presentations and the call for papers is now open. The deadline is December 4th (at 5pm PST for people who really like to come down to the wire). At this point only an abstract is required.

There… Read More

This year’s Renesas DevCon in Orange County, CA kicked off yesterday with an impressive lineup of speakers, record attendance, and an increased focus on automotive.

“TheAuto Industry Speaks,” an Expert Panel organized by Martin Bakerof Renesas, featured:

- Yoichi Yano, RenesasExecutive VP and Member of the Board, who early

…

Read More

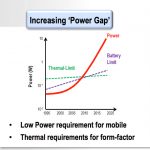

Last week I attended the Ansys/Apache seminars on “Dimensions of Electronic Design.” The two big challenges as we go down to 28nm and 20nm and below are keeping power manageable and keeping reliability up.

The big challenge with power is that we can put so much stuff on a die and clock it so fast that the power is exceeding… Read More

Intel announced its quarterly results a couple of days ago. They had previously downgraded 3rd quarter sales estimates but they managed to beat the downgraded numbers. If you look at the transcript of the call (I didn’t listen live) you’ll see very little mention of mobile and Atom. This is bad news for Intel. Its core… Read More

The early first generation analog standards all used a technique known as Frequency Division Multiple Access (FDMA). All this means is that each call was assigned its own frequency band in the radio spectrum. Since each band was only allocated to one phone, there was no interference between different calls. When a call finished… Read More

Virtuoso Has Twinsby Paul McLellan on 10-18-2012 at 6:01 pmCategories: Cadence, EDA

Cadence has apparently announced that going forward the Virtuoso environment is going to be split into two and offered as two separate code-streams, the current IC6.x and a new IC12.x. The idea is to introduce a new product with features that were specifically developed for new technologies such as double patterning aware layout… Read More

At the Linley conference last week I ran into Gordon Brebner of Xilinx. He and I go a long way back. We had adjacent offices in Edinburgh University Computer Science Department back when we were doing our PhDs and conspiring to network the department’s Vax into the university network over a two-week vacation. We managed to … Read More

There’s a nice article on timing closure by Dr. Jason Xing, Vice President of Engineering at ICScape Inc. on the Chip Design website. Not familiar with ICScape? Paul McLellan called ICScape the The Biggest EDA Company You’ve Never Heard Ofand Daniel Payne did Schematic, IC Layout, Clock and Timing Closure from ICScape at… Read More

SpringSoft, soon to be part of Synopsys but officially still a separate company for now, just announced that Laker[SUP]3[/SUP], the third generation of their layout product family, is featured in TSMC’s 20nm Custom Reference Flow.

Laker 20nm advancements include new double patterning-aware design and voltage-dependent… Read More

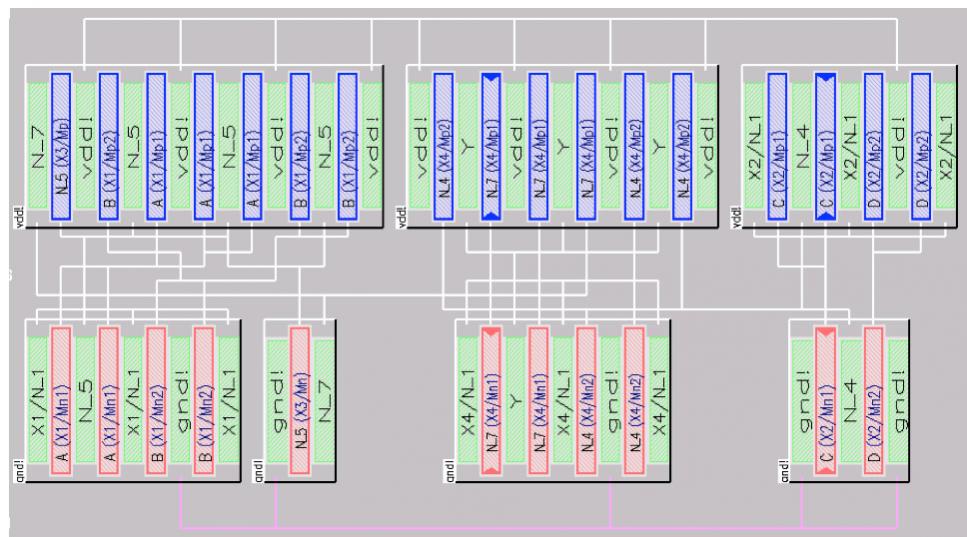

My new iPad lasts about 10 hours on a single charge and the A5X processor is designed with a 45nm process from Samsung. Processor chips for tablets like this use a multi-voltage IC design flow to reduce total power by:… Read More