You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Simon Favre, one of our Calibre Technical Marketing Engineers, presented a paper on Critical Area Analysis and Memory Redundancy at the 2010 IEEE North Atlantic Test Workshop in Hopewell Junction, NY, just up the road from Fishkill. As Simon says…

Fishkill, New York. IBM is in Fishkill. IBM invented Critical Area Analysis in what,… Read More

Bill Wiseman of McKinsey & Company presented “Waking up to the new normal, the world economy after the great recession” at a recent ITAC GSA Conference. Bill supports my previous semiconductor financial predictions in great and graphical detail.

In the United States: unemployment claims are up, home sales are down without… Read More

According to an amended 13S filing, you now own 7.9% of Mentor Graphics, up from 6.86% disclosed on May 27th. Just what are you thinking!?!?!? Clearly you are a smart guy and you pretty much invented the game of corporate raidership, but EDA? Mentor Graphics? EDA does not need you, Mentor Graphics does not need you, I do not need you … Read More

Federal Reserve Chairman Ben Bernanke recently testified before Congress that the U.S. economy is recovering, and he predicts the nation will not experience a double-dip recession, or as I predicted a big “V” then a small “v” in my blog: China Semiconductor Bubble.

Bill Jewel from Semiconductor Intelligence agrees with Bernanke:… Read More

Overshadowing the acquisition of Denali by Cadence, Synopsys, the #2 semiconductor IP provider acquires Virage Logic, the #3 IP provider. Virage brings the #1 embedded SRAM, #1 BIST, #1 Logic Libraries, #1 DDR, #1 NVM, the ARC CPU cores and audio/video interface technology, and all the AMS IP from the NXP acquisition.

Under the… Read More

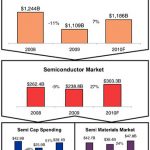

In a previous blog, Black Friday and the Predicted Semiconductor Shortages, I reported that total semiconductor manufacturing capacity is shrinking as older fabs close and new ones ramp up even slower than expected, resulting in a record reduction of total wafer capacity and silicon allocation starting in 2010. DRAM shortages… Read More

As you may know I enjoy poking fun at the current state of semiconductor design and manufacture media; sloppy reporting, editors with little or no actual semiconductor experience taking corporate marketing spins on news/events and passing it along as fact.

Last week it was the EETimes parroting the Samsung foundry business press… Read More

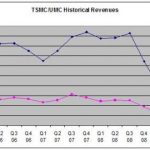

My visit to Taiwan last week was very encouraging. No earthquake, no typhoon, and both TSMC and UMC again posted record financial results, giving a peek into what 2011 has in store for us semiconductor professionals around the world.

A transcript from the TSMC earnings call can be foundhere, the UMC transcript is here. The TSMC transcript… Read More

In the name of blogging and increased transparency lets talk about wafer allocation, because it’s coming, believe it. There is already a significant delta between wafer demand and manufacture due to record low inventory levels and the exploding semiconductor demand in China. Both TSMC and UMC posted good July sales numbers: … Read More

EDA is DEADby Daniel Nenni on 05-23-2009 at 12:12 amCategories: EDA

Years ago I bought my ancestral home, the house where my beloved grandparents lived, the place in which I grew up. It was more an emotional investment than a financial one, much more. After completely renovating it with my keyboard hardened hands, reliving much of my childhood, I joined the ranks of the slum lords and rented the house… Read More