This was the 19[SUP]th[/SUP] annual TSMC Symposium and by far the best I have attended. Finally tired of the misinformation that plagues our industry, TSMC set the record straight with wafer and silicon correlated data. TSMC shipped more than 88 MILLION logic wafers in 2012, more than any other semiconductor company, that gives… Read More

Tag: semiconductor

How to make ESL really work – see EDPS

The Electronic Design Process Symposium (EDPS) is April 18 & 19 in Monterey. The workshop style Symposium is in its 20[SUP]th[/SUP] year. The first session is titled “ESL & Platforms”, which immediately follows the opening Keynote address by Ivo Bolsens, CTO of Xilinx.

In his keynote presentation Ivo will present how… Read More

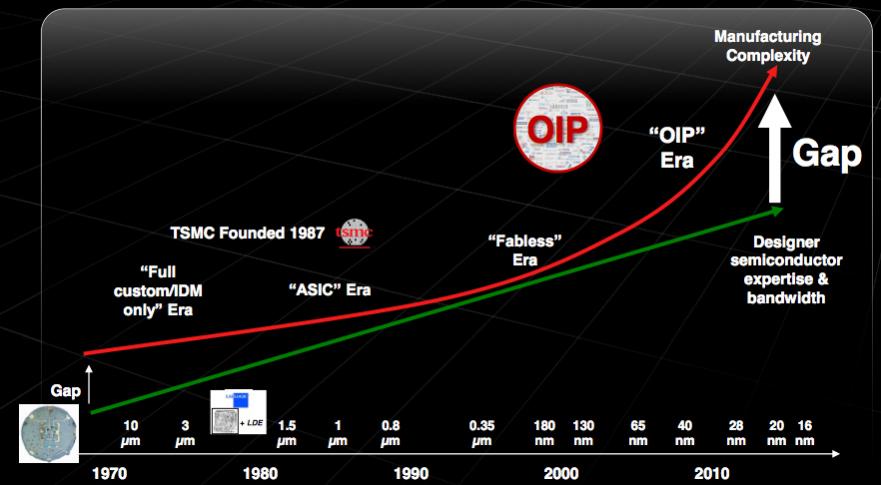

Fabless to OIP

Suk Lee drew the short straw at the TSMC Symposium yesterday, with the 5pm slot. Not only late in the day but between all the attendees and free beer. The morning sessions had been standing room only, with several hundred standees (as they call them on muni around here, but isn’t a standee really someone being stood on?). But … Read More

Mentor U2U, Not Your Father’s User Conference

I talked to Michael Buehler-Garcia about the changes Mentor is making to U2U, their user conference. It is in San Jose on April 25th at the DoubleTree.

Firstly, there are 3 great keynotes, two of whom I’ve seen speak before and can unreservedly recommend. Unfortunately I’m traveling that week and won’t be able… Read More

Cadence Sues Berkeley Design Automation

Cadence has brought a suit against Berkeley Design Automation for, as far as I can see, integrating their AFS circuit simulator with the Virtuoso Analog Design Environment (ADE) without using the (licensed) Oasis product. Since BDA is (actually was) a member of the Cadence Connections program, they have to abide by the contract… Read More

GlobalFoundries in Singapore

I hosted a webinar today for GlobalFoundries. Yes, I know that today was TSMC’s Technology Symposium, we weren’t that smart when we picked the date. It was basically a “fireside chat” with me as the moderator asking the questions and Paul Colestock and Aabid Husain as my guests. We actually did it at Cadence… Read More

Manage your IC’s Stress for right performance

As we have moved towards lower process nodes to improve performance of ICs with higher density and functionality, many manufacturing effects have appeared which can render ICs useless, even though the layout design could be correct as per traditional design rules. What is more worrisome is the variability of these effects which… Read More

How Long Does it Take to Go From a Muddy Field to Full 28nm Capacity?

TSMC has a lot of capacity. Not just that, it has a lot more under construction. It currently has 3 300mm Gigafabs, fabs 12,14 and 15 (there doesn’t seem to be a 13). This morning, Dr Wang, who is TSMC’s VP of 300mm operations told us about the expansion plans. Currently fab 15 phase 3 and 4, and fab 12 phase 3 are to be ramped… Read More

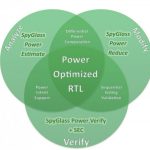

RTL Power Optimization

More so than most aspects of design, power reduction suffers from a paradox that early in the design cycle when the gains are the largest, the accuracy of power estimation is the lowest, and then late in the design cycle, when everything is known pretty much exactly it is too late to make anything other than trivial optimizations. … Read More

SoC Power Integrity Challenges

At DAC in 2012 I visited a few dozen EDA companies and blogged 32 articles, however I didn’t get to see what Apache Design (now a subsidiary of ANSYS) had to say. I did have 20 minutes today to watch their latest video on SoC Power Integrity Challenges and decided to share what I learned. If you want to watch the video at Tech Online,… Read More