You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target … Read More

When we talk about parasitic, we talk about post layout design further expanded in terms of electrical components such as resistances and capacitances. In the semiconductor design environment where multiple parts of a design from different sources are assembled together into highly complex, high density SoC, imagine how complex… Read More

Since power has acquired a prime spot in SoCs catering to smart electronics performing multiple jobs at highest speed; the semiconductor design community is hard pressed to find various avenues to reduce power consumption without affecting functionality and performance. And most of the chips are driven by multiple clocks that… Read More

Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

In one of my favorite movies, Brad Pitt utters the only question that matters in baseball or technology management in the face of uncertainty: “Okay, good. What’s the problem?” Not surprisingly in that scene, as the question circles the table of experts used to doing things the old way, not a single one can answer it correctly in the… Read More

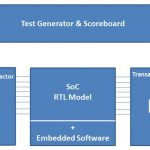

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More

I am talking about the health of electronic and semiconductor design, which if made sound at RTL stage, can set it right for the rest of the design cycle for faster closure and also at lesser cost. Last week was the week of ITC(International Test Conference) for the Semiconductor and EDA community. I was looking forward to what ITC… Read More