This white paper about Cadence innovative mixed-signal IP concept “Cadence Multi-Link PHY IP (SerDes, Analog Front-end, and DDR) to Design SoC Platform breaking the “Business Gap” on 14/16FF” describe the problem, the emergence of a “business gap” linked with incredibly high development cost when targeting most advanced … Read More

Tag: phy ip

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

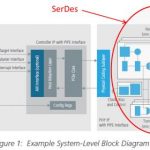

Don’t Mess with SerDes!

SerDes stands for Serializer/Deserializer, and SerDes is a serious piece of design, requiring an extremely experienced team of analog engineers (below 10 years’ experience, you’re still a quasi-beginner). Better to rely on an analog guru to draw the SerDes architecture and manage the team! Why does SerDes is becoming more and… Read More

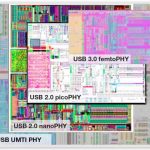

USB 3.0 IP on FinFET may stop port pinching

Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

High Quality PHY IPs Require Careful Management of Design Data and Processes

In last few years IP design has grown significantly compared to the rest of the semiconductor industry. There are newer IP start-ups opening across the world, particularly in India and China. Amid this rush, I wanted to understand the actual dynamics pushing this business and whether all of these IPs follow quality standards. … Read More

Emerging Trend – Choose DRAM as per Your Design Need

Lately I was studying about new innovations in memory world such as ReRAM and Memristor. As DRAM (although it has become a commodity) has found its extensive use in mobile, PC, tablet and so on, that was an inclination too to know more about. While reviewing Cadence’s offering in memory subsystems, I came across this whitepaperwhich… Read More

Should an IP vendor become a PHY IP Dealer?

This is not a theoretical question. Imagine that you are developing and selling digital IP, like Interface Controller, PCI Express or USB 2.0 or 3.0, or MIPI Camera Serial Interface (CSI) or Display Serial Interface (DSI). If you look at companies like Synopsys, they have built their success on the “Integrated Interface IP” concept.… Read More

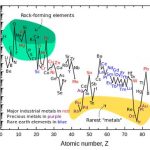

Rare earth syndrome: PHY IP analogy

If you ask to IP vendors selling functions, PHY or Controller, supporting Interface based protocols which part is the master piece, the controller IP only vendors will answer: certainly my digital block, look how complex it has to be to support the transport and logical part of the protocol! Just think about the PCI Express gen-3… Read More

Is PHY IP really strategic? Just take a look at the various legal offensives running these days…

Last week, at the same time I was writing a blog about PHY IP market, claiming that this market was shaken, several events happened – not on the pure business side, but on the legal side. This means that I will have to carefully check before using each word of this blog!

If you remember, the blog conclusion was focusing on V Semiconductor,… Read More

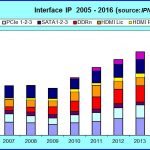

Such a small piece of Silicon, so strategic PHY IP

How could I talk about the various Interface protocols (PCIe, USB, MIPI, DDRn…) from an IP perspective and miss the PHY IP! Especially these days, where the PHY IP market has been seriously shaken, as we will see in this post, and will probably continue to be shaken… but we will have to wait and look at the M&A news during the next … Read More