Around the mid-2000’s the performance component of Moore’s Law started to tail off. That slack was nicely picked up by architecture improvements which continue to march forward but add a new layer of complexity in performance optimization and verification. Nick Heaton (Distinguished Engineer and Verification Architect at… Read More

Tag: performance

Expedera Proposes Stable Diffusion as Benchmark for Edge Hardware for AI

A recent TechSpot article suggests that Apple is moving cautiously towards release of some kind of generative AI, possibly with iOS 18 and A17 Pro. This is interesting not just for Apple users like me but also for broader validation of a real mobile opportunity for generative AI. Which honestly had not seemed like a given, for multiple… Read More

Breakthrough Gains in RTL Productivity and Quality of Results with Cadence Joules RTL Design Studio

Register Transfer Level (RTL) is a crucial and valuable concept in digital hardware design. Over the years, it has played a fundamental role in enabling design of complex digital chips. By abstracting away implementation details and providing a clear description of digital behavior, RTL has contributed significantly to the… Read More

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

NoC-Based SoC Design. A Sondrel Perspective

Why are NoCs important in modern SoCs and what are best design practices for using NoC? As always, a great place to start is the perspective of an SoC design organization which depends on pumping out high performance designs. Sondrel is a turnkey ASIC service provider, covering the spectrum from system design to silicon supply. … Read More

A Next-Generation Prototyping System for ASIC and Pre-Silicon Software Development

Every now and then, disruptive technology is brought to market, challenging the way things have been done to that point. We are all familiar with many such technologies. The rhetorical question is, how many of us were aware, recognized and acknowledged those technologies before they became well established? For example, a startup… Read More

Optimizing High Performance Packages calls for Multidisciplinary 3D Modeling

For all the time we spend thinking and talking about silicon design, it’s easy to forget just how important package design is. Semiconductor packages have evolved over the years from very basic containers for ICs into very specialized and highly engineered elements of finished electronic systems. They play an important role … Read More

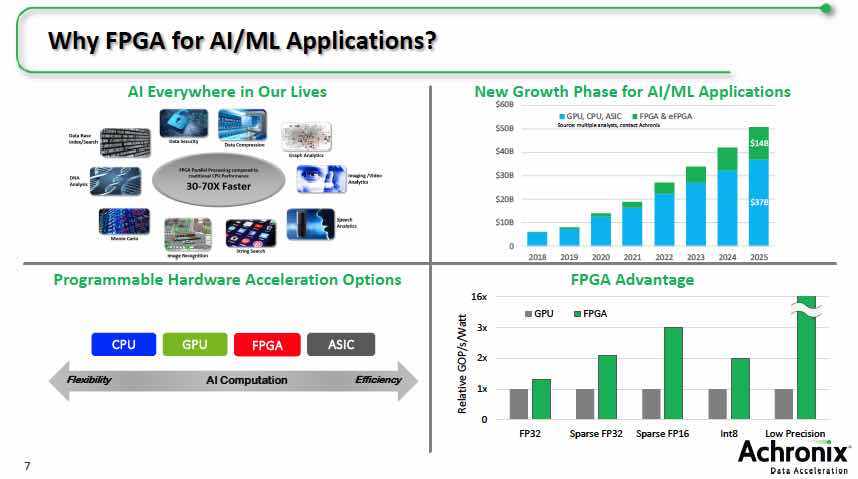

Embeddable FPGA Fabric on TSMC 7nm

With their current line-up of embeddable and discrete FPGA products, Achronix has made a big impact on their markets. They started with their Speedster FPGA standard products, and then essentially created a brand-new market for embeddable FPGA IP cores. They have just announced a new generation of their Speedcore embeddable… Read More

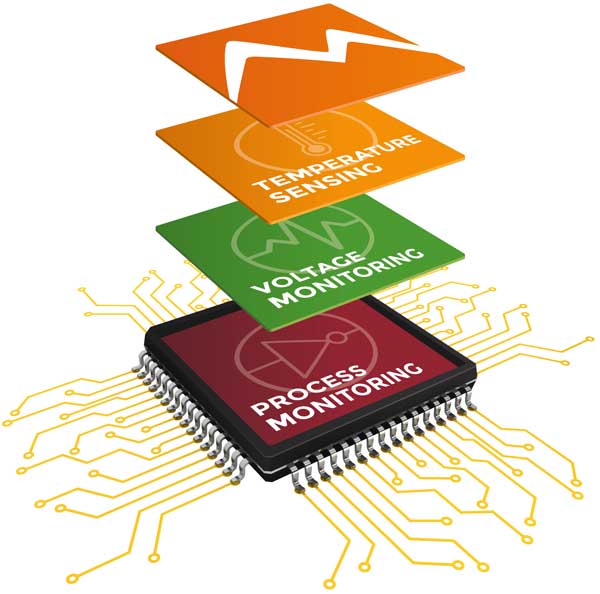

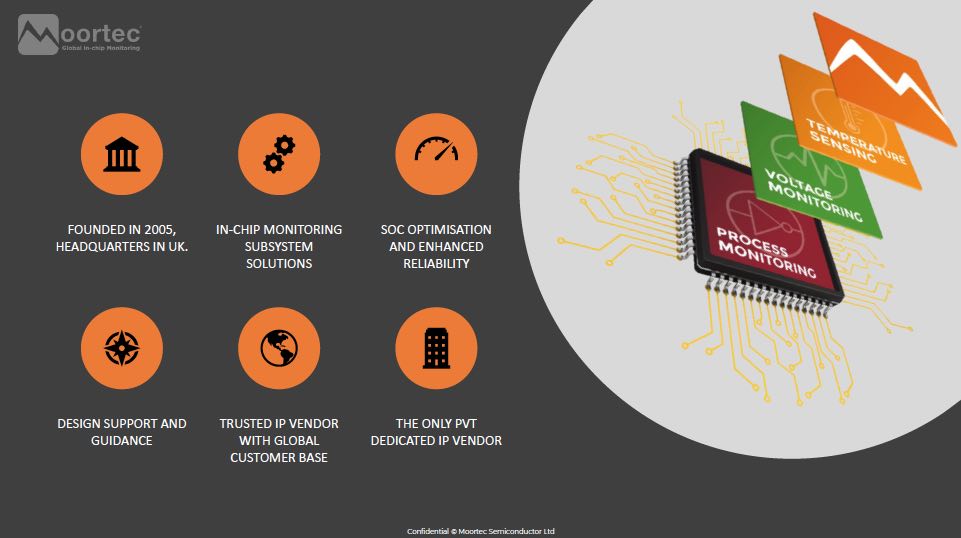

Making AI Silicon Smart with PVT Monitoring

PVT – depending on what field you are in those three letters may mean totally different things. In my undergraduate field of study, chemistry, PVT meant Pressure, Volume & Temperature. Many of you probably remember PV=nRT, the dreaded ideal gas law. However, anybody working in semiconductors knows that PVT stands … Read More

A Smart Way for Chips to Deal with PVT Issues

We have all become so used to ‘smart’ things that perhaps in a way we have forgotten what it was like before many of the things we use day to day had sensors and microprocessors to help them respond to their environment. Cars are an excellent example. It used to be commonplace to run down your battery by leaving your lights on. Now cars … Read More